Other Parts Discussed in Thread: TAS2557, TMS320F28015, , TAS2505, TAS2563, TAS2552, TAS2555

Hi,

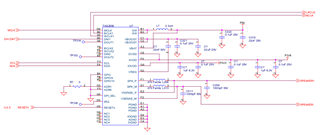

I am evaluating the TAS2559 in hopes of using it (or the TAS2557) to replace a Cirrus Logic/Wolfson WM9081 in an existing design. The WM9081 uses the following configuration:

- Input clock is 15 MHz. This clock comes from a TMS320F28015, and is connected to the MCLK input of the WM9081.

- The WM9081 divides the 15 MHz clock by 2 to generate an internal FLL reference clock of 7.5 MHz.

- The FLL of the WM9081 is used to generate an internal CLK_SYS of 11.29 MHz.

- The WM9081 generates BCLK of 705.62 kHz and a LRCLK of 22050 Hz. BCLK and LRCLK are outputs from the WM9081 to an FPGA.

- The FPGA uses BCLK and LRCLK to generate a DACDAT output that goes to the WM9081.

- The WM9081 converts the DACDAT I2S data stream from the FPGA into mono audio with a class D amp.

- The I2C interface of the TMS320F28015 is used to configure the WM9081 and to control the volume during operation.

The TAS2557 or TAS2559 look like possible replacements for the WM9081, but configuration looks to be a problem due to our use of non-standard clocking and the limited documentation for TAS series devices. Hence the following questions:

- Is the TAS2557 or TAS2559 an appropriate choice? Note that we have an immediate need. Better devices that are out of stock are not a solution.

- Are the TAS2557 and TAS2559 pin compatible if only one I2S interface is needed?

- Can the PLL be configured to generate a suitable clock for a 22050 sample rate given our 15 MHz input?

- Is there any official documentation for the PLL? I see that another user managed to reverse engineer a portion of the PLL (tas2559 pll and clocking configuration). (I have to say that it's pretty disappointing that he had to do that.)

- Assuming the PLL can be used to generate 11.29 MHz from 15 MHz, what are the PLL constraints that need to be observed (VCO Fmax, Fmin, etc.)?

Note that while many of the DSP features of these devices look very interesting, our immediate need is for I2S to mono audio out to a 4 ohm speaker. We would be using ROM Mode 1 for the foreseeable future.

Currently I have a TAS2559EVM here and I was hoping to be able to tack some wires onto our existing WM9081 board in order to try out the TAS2559, but PPC3 seems very limited in terms of clocking configuration. At this point it seems I'd be better off just poking registers over I2C, but I don't want to head down that path without knowing that the TAS2557 or TAS2559 will do what I want.

Thanks for your help.

galen