Hi team,

my customer found there's no sound output, and we don't have EVM to debug now

would you help debug on this? they're quite urgent

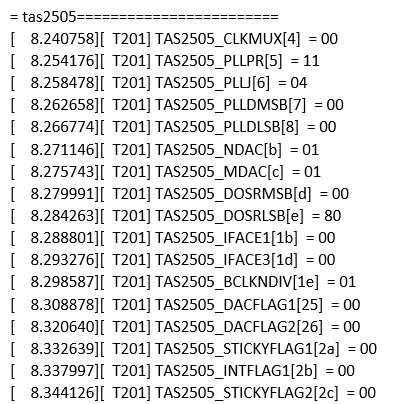

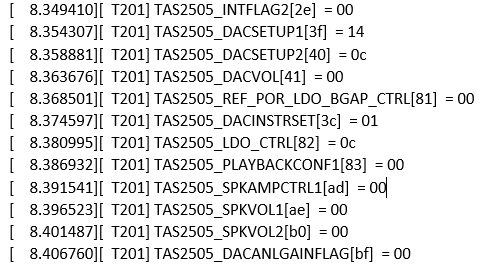

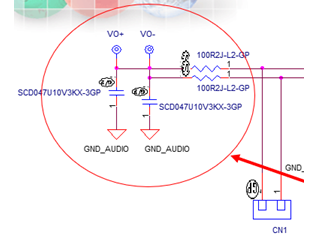

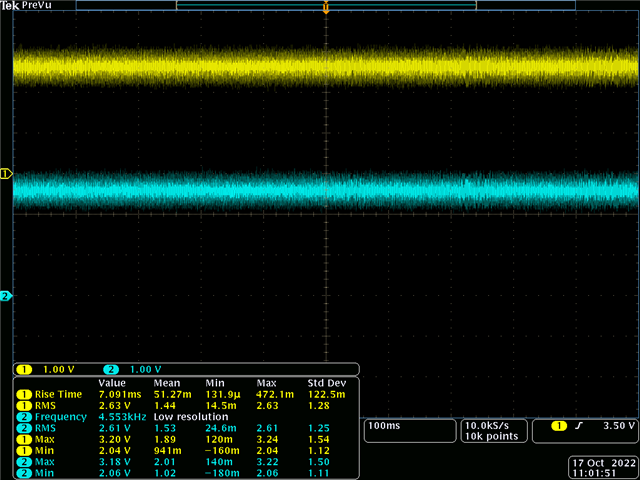

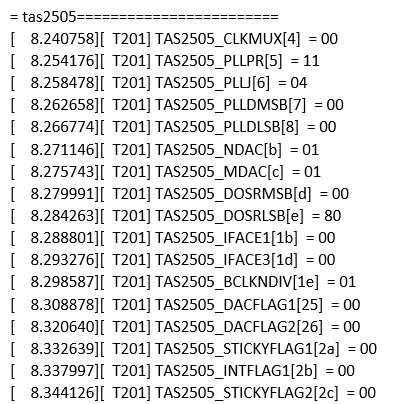

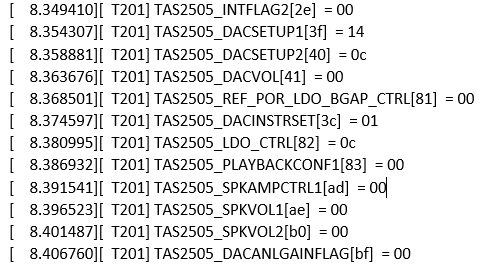

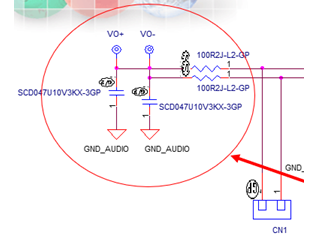

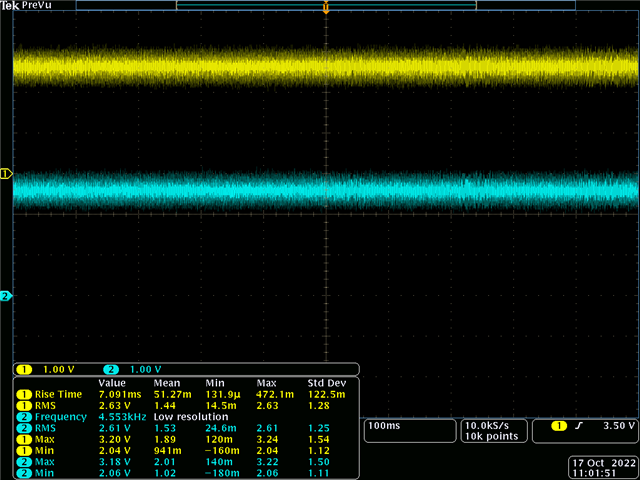

below is the schematic , I2C log and output waveform,

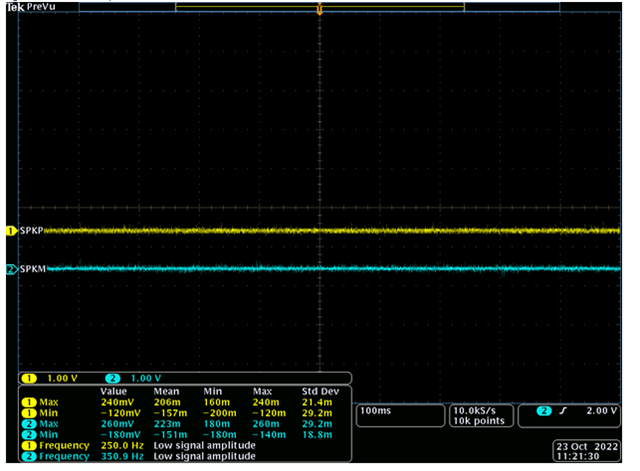

they measure at this two point after low pass,

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

my customer found there's no sound output, and we don't have EVM to debug now

would you help debug on this? they're quite urgent

below is the schematic , I2C log and output waveform,

they measure at this two point after low pass,

Hi Fred,

I've got some questions on the schematic and test:

Best regards,

-Ivan Salazar

Applications Engineer

Hi Ivan,

they connect LDO_SEL to SPKVDD, but still no change.

but I'm confused that datasheet say LDO_SEL should connect to GND

I'll update the rest you requested later

Hi Fred,

Can you please also share the input clock frequencies to double check the register configuration? We'll need MCLK (if used), BCLK and WCLK.

Regarding the LDO_SEL pin, at some point we encouraged customers to not use the internal LDO due to some known issue that affected a few devices in some specific application conditions. This is being handled on a new revision that will be released soon.

However if your problem is observed on all units, then it should not be related to this LDO and you should still be able to use it.

Best regards,

-Ivan Salazar

Applications Engineer

Hi Ivan,

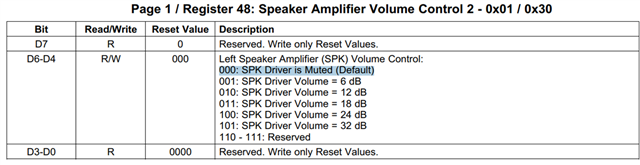

have you looked into the I2C log?

our register 48 is defaulted muted, is this the problem?

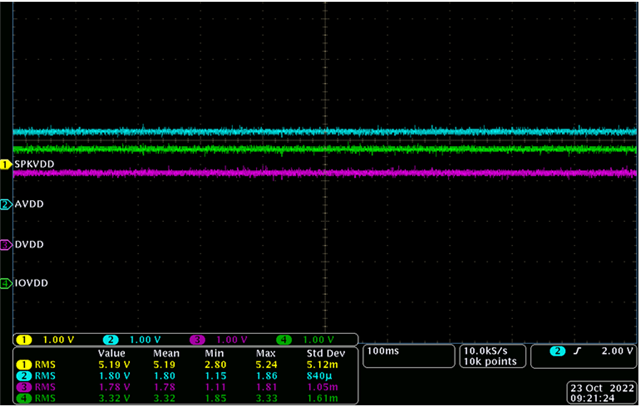

update the voltage you want,

Hi Fred,

After review of the I2C log, it doesn't seem right:

They can use the GUI example script as baseline:

# Playback Class-D # Page switch to Page 0 W 30 00 00 # Assert Software reset W 30 01 01 # Page Switch to Page 1 W 30 00 01 # LDO output programmed as 1.8V and Level shifters powered up. W 30 02 00 # Page switch to Page 0 W 30 00 00 # Dac Instruction programming PRB #1 W 30 3c 01 # CODEC_CLKIN=MCLK.MCLK should be 12.288MHz W 30 04 00 # Codec Interface control Word length = 16bits.BCLK&WCLK inputs.I2S mode. W 30 1b 00 # Data slot offset 00 W 30 1c 00 # DAC NDAC Powered up, NDAC=1 W 30 0b 81 # DAC MDAC Powered up, MDAC=2 W 30 0c 82 # DAC OSR(9:0)-> DOSR=128 W 30 0d 00 # DAC OSR(9:0)-> DOSR=128 W 30 0e 80 # Only LDAC powered up.Dac path setup LDAC data Mono of LDAC and RDAC. RDAC data disabled.Soft step 1 per Fs. W 30 3f B0 # DAC volume for Left channel not muted.Right DAC muted. W 30 40 04 # LDAC digital gain 0dB W 30 41 00 # Page Switch to Page 1 W 30 00 01 # Master Reference Powered on W 30 01 10 # Output common mode for DAC set to 0.9V (default) W 30 0a 00 # LDAC AFIR is 6th order FIR filter and Powered up. W 30 03 00 # SPKL attn. Gain =0dB W 30 2E 00 # SPKL driver PGA Gain=6.0dB W 30 30 10 # SPK OSCP enabled , OCP Degltich=4, OTP enabled , OTP Deglitch=5 W 30 52 00 # SPK powered up W 30 2D 02

Best regards,

-Ivan Salazar

Applications Engineer