Dear e2e support,

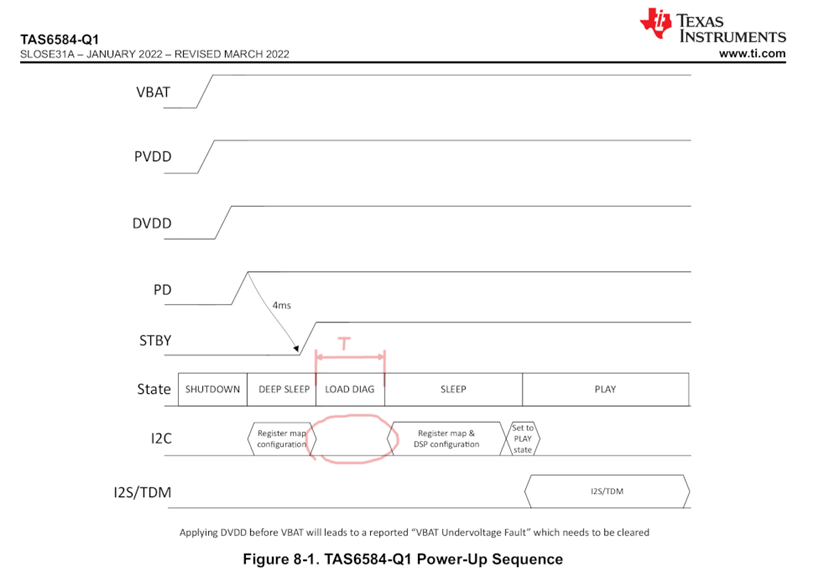

In Figure 8-1, there is this timing diagram:

During the LOAD DIAG state, no communication is made to i2c. This raises some questions:

- Does TAS ignores all communication during that state?

- If I ask TAS for a state change during LOAD DIAG, is it latched and will it be applied at the end, or is it just ignored?

- Assuming each channel has one speaker connected, how long can the LOAD DIAG state last?

Regards,