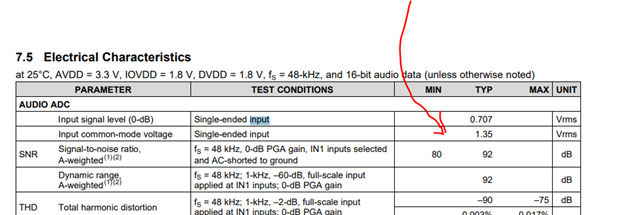

Part Number: TLV320ADC3100

Other Parts Discussed in Thread: TLV320ADC3120

Hi,

We are using the TLV320ADC3100 audio codec for our project. We write in the register first, and then we verify it by reading the registers. However, the value we get after reading the register is different from what we wrote there. Is there anything we have to take care for I2C peripheral?

We have configured the Audio codec in master mode and our desire output is:

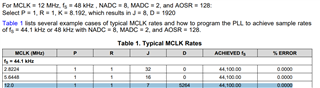

BCLK: 2.8224Mhz

WCLK: 44.1khz

Sample Size: 32-bit

For that we have given the MCLK of 12.288Mhz.

Also, below are the configured register's value.

ADC310X_PAGE_SELECT - 0x00 // Page - 0 selected

ADC310X_RESET - 0x01 // Soft Reset

ADC310X_CLK_GEN_MUX - 0x00 // Clock Generation

ADC310X_PLL_PR_VAL - 0x91 // PLL_CLK - 90.3168

ADC310X_PLL_J_VAL - 0x07 // J - 7

ADC310X_PLL_D_VAL_MSB - 0x0D //

ADC310X_PLL_D_VAL_LSB - 0xAC // Combination of MSB and LSB is 3500 for D

ADC310X_NADC_CLK - 0x88 // NADC - 8

ADC310X_MADC_CLK - 0x82 // MADC - 2 as per our calculations

ADC310X_AOSR - 0x80 // Oversampling - 128

ADC310X_ADC_IADC - 0x20 // IADC - 32

ADC310X_ADC_INTF_CTRL_1 - 0x3C // i2s for adc interface with 32 bits sample size, both BCLK and WCLK as output

ADC310X_ADC_INTF_CTRL_2 - 0x06 // BDIV_CLKIN = ADC_CLK and both are active even with the codec powered down

ADC310X_BLCK_N_DIV - 0x82 // Value is 2 as per our calculations.

ADC310X_ADC_PROC_BLK- 0x01 // ADC signal processing block PRB_R1

ADC310X_PAGE_SELECT - 0x01 // Page - 1 selected

ADC310X_PGA_ANALOG_L - 0x00 // Left PGA gain = 0 dB and muted

ADC310X_PGA_ANALOG_R - 0x00 // Right PGA gain = 0 dB and muted

ADC310X_INPUT_SEL_PGA_L_1 - 0xfc // Left ADC Input selection for Left PGA = IN1L(P) as Single-Ended

ADC310X_INPUT_SEL_PGA_R_1 - 0xfc // Right ADC Input selection for Right PGA = IN1R(M) as Single-Ended

ADC310X_PAGE_SELECT - 0x00 Page - 2 selected.

ADC310X_ADC_DIGITAL - 0xc2 // Power-up Left ADC and Right ADC

ADC310X_ADC_VOL_CTRL - 0x00 // Unmute digital volume control and set gain = 0 dB

Please suggest some suggestions.

Thanks & Regards

Lakshita

.

.