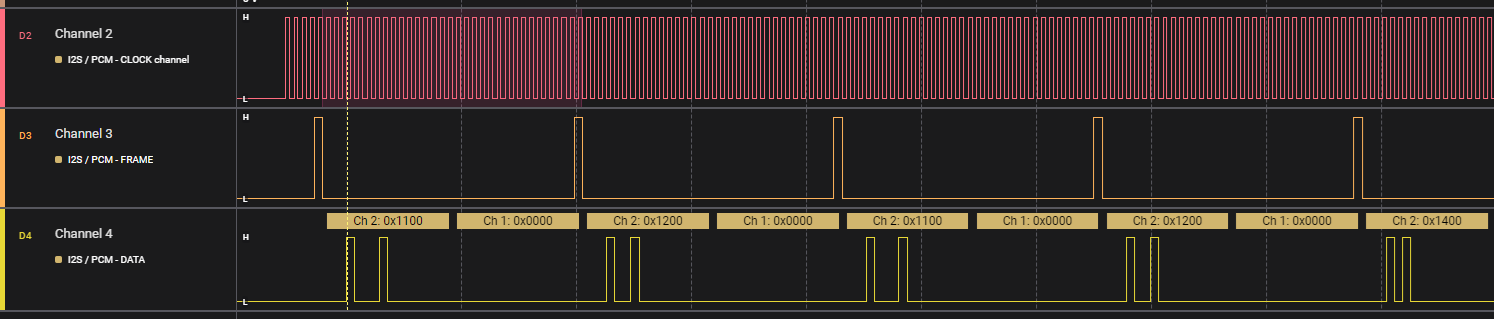

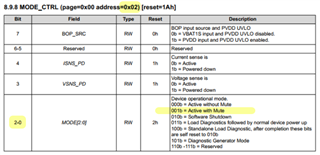

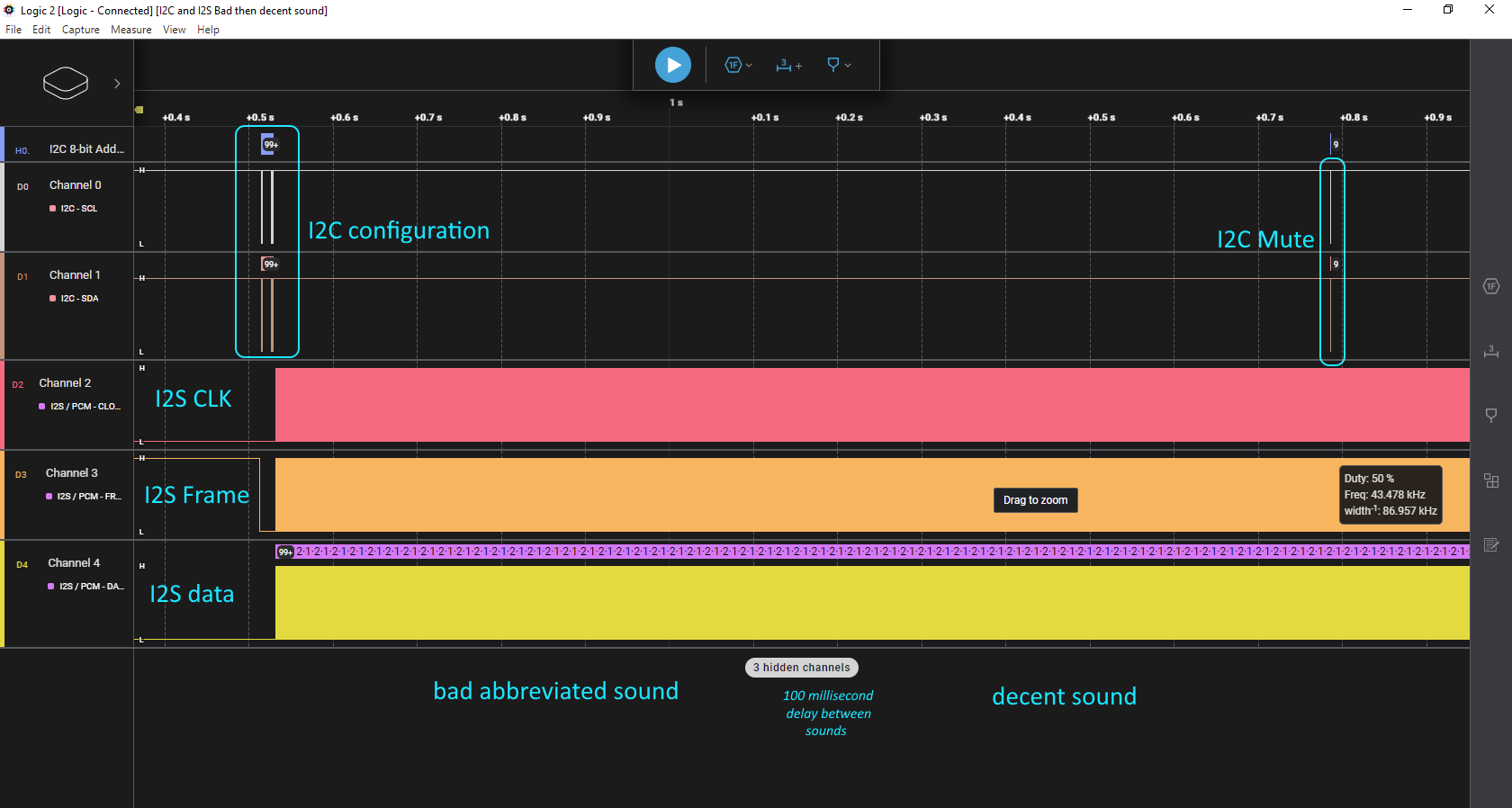

Does the I2S/TDM interface to this device require all 8 channels or can you send data for 1 channel only?

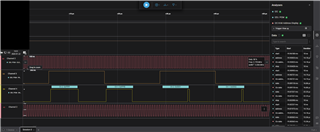

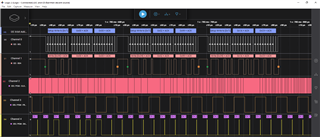

I see the demo sends data for 8 channels between FSYNC pulses. We are trying to send data for only 1 channel since we don't need more than one channel, but as of now it doesn't appear to be working.