- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Working with the TLV320DAC3100 dev board, the ADC gain control in the TI GUI does not affect the audio.

Is this a bug in the GUI or have I missed something?

Also, how do I capture the I2C messages of the control changes I make?

Hi Bruce,

Can you confirm if using AIC3100 or DAC3100?

Only AIC device features ADC.

Best regards,

-Ivan Salazar

Applications Engineer

The chip on the dev board says DAC3100 yet I am able to get mic input signal to show up on the USB interface. I can control which channel is mixed into the ADC input but I cannot adjust the gain.

My main issue is translating the GUI control actions (other than the init string) to I2C command code.

Ivan,

I guess I have made a big mistake (twice now) and ordered the DAC3100 dev board.

My target device in my product design is the AIC3100 and I have evidence from testing that the initialization code that I got from the GUI and dev board is working (at least it turns on the power to the class D amp)

Will the GUI still send I2C commands to the DAC3100 board that I can read with a logic analyzer to adjust the audio input aspects of the AIC3100?

I do not want to spend another $250 for another dev board so how do I just translate the I2C control messages for my target design?

Also, what is the "30" in this message

# NDAC is powered up and set to 4

w 30 0b 84

The Datasheet for the TLV320AIC3100 says "The I2C address assigned to the TLV320AIC3100 device is 001 1000"

The initialization script starts each write message with 0x30

001 1000 translates to 0x18

Which address value do I send?

Hi Bruce,

The value of 30 is the device I2C address, note this is 8-bit address, adding a 0 at the LSB.

You may still be able to use the GUI at least to get the commands, even if the device is not actually enabling/using the ADC side, or with the EVM disconnected:

Best regards,

-Ivan Salazar

Applications Engineer

OK

I have confirmed my initialization is being sent correctly by my CPU.

Even though the Dev Board is a DAC3100, the GUI still is sending initialization that includes ADC setup and when connected to the dev board by USB, it shows AIC3100 in the title bar.

Is the I2C setup entirely controlled by the master clock coming from (my DSP/CPU)? Or do I still need to set the proper wordlength? My DSP is currently generating a 12MHz MCLK.

What are the default values for the I2C setup?

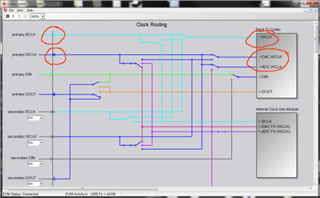

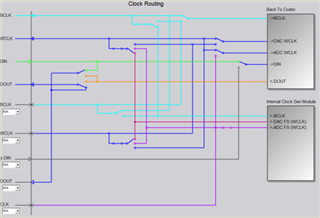

The GUI shows the BCLK and WCLK as if they are outputs?

Is the default state of the AIC3100 I2S master or I2S slave?

If it is a master, how do I change it to be a slave?

Hi Bruce,

Default is slave mode for I2S interface.

You do need to configure the internal clock settings according to the clocks from the system.

Best regards,

-Ivan Salazar

Applications Engineer

I am currently using the TLV320AIC23B in my working prototype and needing to convert to the AIC3100

In the AIC23design I am feeding the codec device MCLK, BCLK, LRCLK

The MCLK is 12MHz

The BCLK is 3MHz

The LRCLK is toggling at 46.8KHz

I can change the DSP crystal to 12.288MHz to get standard frequencies (48khz)

What settings would I use for the AIC3100 to use these same clocks?

Sorry to be so brain dead on this issue.

The clock routing diagram does not show any (input or output) from MCLK

Does it matter if I sync to BCLK or MCLK? Does it affect sound quality or jitter?

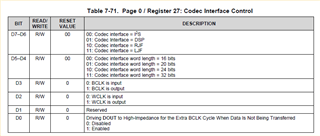

And nothing on the Clock Routing page seems to affect Register 27.

I see no mention of MCLK input option on Table 7-71

Please advise

Hi Bruce,

AIC3100 documentation includes clock tree diagrams and register control details for each of the clock selections and clock dividers.

I'll try to make some time to answer specific questions tomorrow.

Best regards,

-Ivan Salazar

Applications Engineer

Thanks for your continued support.

I’ll cue up my next question.

Since the AUC3100 can sync to either the BCLk or MCLK, is there a preference?

Also, if I have the wrong word length setting, will it not pass audio or will it just sound bad?

Thanks for your continued support.

I’ll cue up my next question.

Since the AUC3100 can sync to either the BCLk or MCLK, is there a preference?

Also, if I have the wrong word length setting, will it not pass audio or will it just sound bad?

Hi Bruce,

OK, I'll try to make time to answer back within next couple of days.

Best regards,

-Ivan Salazar

Applications Engineer

I am reading

7.3.11 Clock Generation and PLL and

7.3.12 Digital Audio and Control Interface

I am finding it hard to understand all the details and interactions.

Given the existing I2S clocks generated by my DSP and the fact that they work properly with the TLV320AIC23B, is there a easier way to determine the correct register settings to use on the AIC3100?

Please Advise

Hi Bruce,

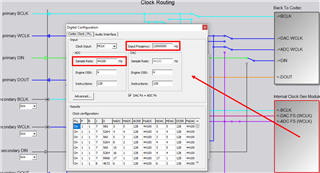

You may use BCLK as clock source, this seems a ratio of 64 compared to WCLK so the PLL configuration should be:

PLL_P = 1

PLL_R = 1

PLL_J = 28

PLL_D = 0

NDAC = NADC = 7

MDAC = MADC = 2

DOSR = AOSR = 128

You should write thes registers to configure the clock tree: 4 through 8, 11 through 14 and 18 through 20.

There's no preference of one clock over the other.

If you have a previous configuration for AIC32, I suggest starting a new thread with the proper part number, either AIC3100 or AIC32 (I'm not supporting either and got assigned to this because it was DAC3100).

Best regards,

-Ivan Salazar

Applications Engineer