- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

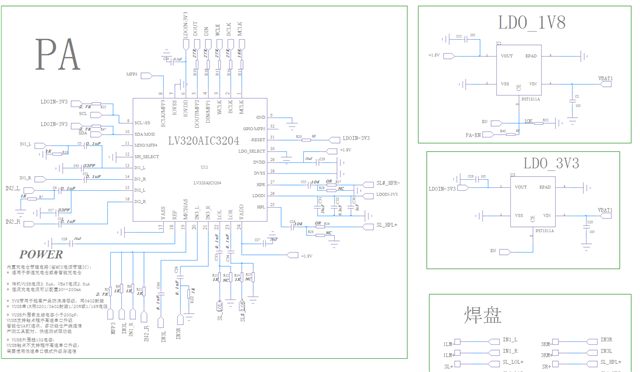

Hello, I want to know the power consumption of the low power mode of TLV320AIC3204. I find that it consumes a lot of power when I use it now. I need to reduce the power consumption while guaranteeing the original function. Below is my register configuration and circuit diagram.

############################################### # Software Reset ############################################### # # Select Page 0 w 30 00 00 # # Initialize the device through software reset w 30 01 01 # ############################################### ############################################### # Clock Settings # --------------------------------------------- #The input clock signal : MCLK = 11.2896 MHz,BLCK = 1.4 MHz, WCLK = 44.1 kHz ############################################### # # Select Page 0 w 30 00 00 # # NADC = 1, MADC = 2 w 30 12 81 82 # ############################################### ############################################### #AGC ############################################### w 30 00 00 w 30 57 7E w 30 56 F0 w 30 58 40 w 30 59 08 w 30 5A 32 w 30 5B 18 w 30 5C 06 w 30 5F 7E w 30 5E F0 w 30 60 40 w 30 61 08 w 30 62 32 w 30 63 18 w 30 64 06 ############################################### ############################################### # Enable Loopback Page 0 register 29 ############################################### # # Loopback enable for stereo audio data w 30 1D 10 # ############################################### ############################################### # Signal Processing Settings ############################################### # # Select Page 0 w 30 00 00 # # Program OSR for ADC to 64 w 30 14 40 # Set the ADC Mode to PRB_R7 w 30 3d 07 # ############################################### ############################################### # Initialize Codec ############################################### # # Select Page 1 w 30 00 01 # # Disable weak AVDD in presence of external # AVDD supply w 30 01 08 # # Enable Master Analog Power Control w 30 02 00 # # Set the input common mode to 0.75V w 30 0a 40 # Select ADC PTM_R1 w 30 3d ff # # Set the input powerup time to 3.1ms (for ADC) w 30 47 32 # # Set the REF charging time to 40ms w 30 7b 01 # ############################################### ############################################### # Recording Setup ############################################### # # Select Page 1 w 30 00 01 #MICBIAS w 30 33 50 # Route IN3L to LEFT_PGA_P with 20K input impedance w 30 34 08 # Route IN3R to LEFT_PGA_N with 20K input impedance w 30 36 08 # Route IN1R to Right_PGA_N with 20K input impedance w 30 37 80 # Route IN1L to Right_PGA_P with 20K input impedance w 30 39 20 # # Unmute Left MICPGA, Gain selection of 6dB to make channel gain 0dB # Register of 6dB with input impedance of 20K => Channel Gain of 0dB w 30 3b 00 # # Unmute Right MICPGA, Gain selection of 6dB to make channel gain 0dB # Register of 6dB with input impedance of 20K => Channel Gain of 0dB w 30 3c 00 # # Select Page 0 w 30 00 00 # # Power up LADC/RADC w 30 51 c0 # # Unmute LADC/RADC w 30 52 00 # ############################################### ############################################### # High Performance Stereo Playback # --------------------------------------------- # PowerTune mode PTM_P3 is used for high # performance 16-bit audio. For PTM_P4, # an external audio interface that provides # 20-bit audio is required. # # For normal USB Audio, no hardware change # is required. # # If using an external interface, SW2.4 and # SW2.5 of the USB-ModEVM must be set to # HI and clocks can be connected to J14 of # the USB-ModEVM. # # Audio is routed to both headphone and # line outputs. ############################################### ############################################### # Clock Settings # --------------------------------------------- # The input clock signal : MCLK = 11.2896 MHz,BLCK = 1.4 MHz, WCLK = 44.1 kHz: MCLK = 11.2896 MHz, ############################################### # # Select Page 0 w 30 00 00 # # NDAC = 1, MDAC = 2 w 30 0b 81 82 # ############################################### ############################################### # Signal Processing Settings ############################################### # # Select Page 0 # w 30 00 00 # # Set the DAC Mode to PRB_P8 w 30 3c 08 # ############################################### ############################################### # Playback Setup ############################################### # # Select Page 1 w 30 00 01 # # De-pop w 30 14 16 # # Route LDAC to HPL/HPR w 30 0c 08 10 # # Route RDAC to LOL/LOR w 30 0e 10 08 # # Power up HPL/HPR and LOL/LOR drivers w 30 09 3c # # Unmute HPL/HPR driver, 0dB Gain w 30 10 00 00 # # Unmute LOL/LOR driver, 0dB Gain w 30 12 00 00 # # Select Page 0 w 30 00 00 # # DAC => 0dB #w 30 41 00 00 # DRC w 30 41 EA EA w 30 44 73 w 30 45 00 w 30 46 B6 # # # Power up LDAC/RDAC w 30 3f d6 # # Unmute LDAC/RDAC w 30 40 00 # ###############################################

Hi Luo,

What kind of power performance are you targeting? The application reference guide for this device contains tables on how to achieve lowest power consumption: https://www.ti.com/lit/ml/slaa557/slaa557.pdf?ts=1725981589824&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FTLV320AIC3204

See sections 2.5.2 and 2.5.3 for details. From what I can see in your script you will likely need to adjust your power tune mode.

Best regards,

Jeff McPherson

the AIC3204 employs the I2C interface and to reduce the power consumption follow the given steps Click here hope it'll solve your problems.