Other Parts Discussed in Thread: TAC5212

Tool/software:

Hi all,

Because my application is a very low power one, I would like to get rid of the PLL of the TAC5212.

My requirements are:

- TAC5212 shall be configured as a controller

- TAC5212 shall accept a clock of 14,745,600-Hz as CCLK

- TAC5212 shall generate FSYNC = 19,200-Hz and BCLK = 1,228,800-Hz

- TAC5212 shall transmit/receive two 32-bits words of data in I2S mode

- Internal PLL of TAC5212 shall be disabled

The ratios are:

R1 = BCLK/FSYNC = 64, R2 = CCLK/FSYNC = 768

To try to fulfill those requirements, I did the following actions:

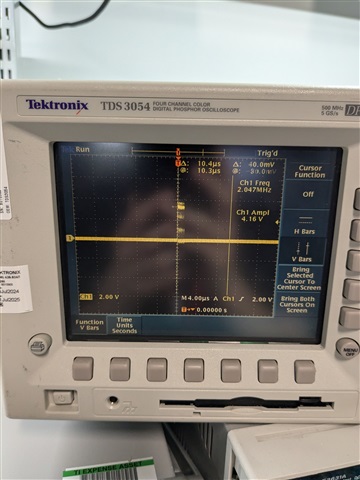

1) As a baseline, run the I2C commands (refer to the picture below) found in the EVM User's Guide, apply a clock (CCLK) of 12,288,000-Hz to GPIO1 and monitor the FSYNC signal with a scope.

I measure: FSYNC = 48,000-Hz as expected.

2) Modify the register 0x32 of page 0: set PASI_SAMP_RATE = 27d = 19,200-Hz. Then modify CCLK to 14,745,600-Hz.

I measure FSYNC = 23,040-Hz. This value was expected too because 14,745,600/12,288,000 = 1.2 thus 19,200*1.2 = 23,040-Hz.

3) Modify the register 0x32 of page 0: set PASI_SAMP_RATE = 28d = 16,000-Hz because 19,200/1.2 = 16,000-Hz.

I measure FSYNC = 19,200-Hz. At this point the generated clocks are correct.

4) Check the status by reading the register 0x3E of page 0.

I read PLL_MODE_STS = 0d = PLL used in integer mode.

5) Modify the register 0x34 of page 0: set PLL_DIS = 1d = PLL is disabled, set AUTO_PLL_FR_ALLOW = 0d = PLL fractional mode disabled.

After the modification, there is no signal on FSYNC.

My question: should I modify others registers after disabling the PLL? Is there an application note describing how to get rid of the PLL?

Thanks in advance for your support.

BR,

Sébastien