Other Parts Discussed in Thread: TLV320AIC3120

Tool/software:

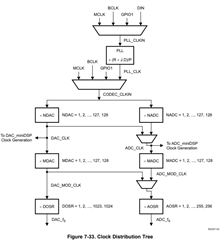

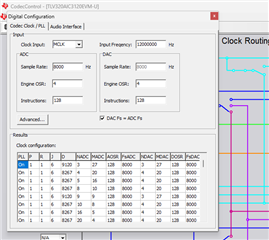

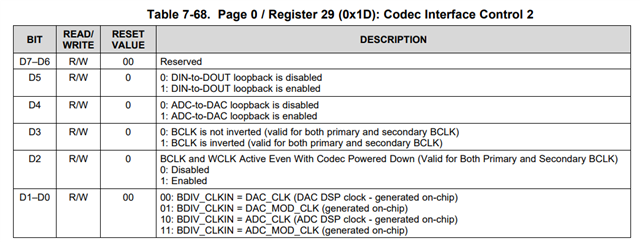

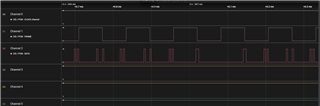

I am working with TLV320AIC3120 audio codec EVM. I want to control the codec and send and receive data through a microcontroller. I was able to calibrate the registers of codec through I2C using the microcontroller. For that, I have used the TP1 and TP2 test points within the codec and connected it to the microcontroller. Now, I want to check the data transfer through I2S lines. For that, I am using the TP3,TP4,TP5,TP6 and TP7 test points and connecting it to the microocntroller. First, I need to check whether data transfer is happening from microcontroller over I2S. In my scenario, microcontroller is the master. So, I have enabled I2S Tx as master with sampling frequency of 8 KHz and channel and word length as 16. But, since the codec is getting MCLK from the internal oscillator within the EVM, the microcontroller cannot provide the MCLK. So, I have just connected MCLK pin from the microcontroller to the corresponding test point in the codec EVM and intiialised it as input pin in the controller, so as to synchronize the audio subsystem of the microcontroller and codec. But still, BCLK and WCLK are coming from the microcontroller. I have tried sending the data and even checked the BCLK and WCLK pins, I am expecing 8 KHz at BCLK and 128 KHz at WCLK pin. But, I am not getting it. I have tried sending some example wave file.

/*******************************************************************************

* File Name: main.c

*

* Description: This is the source code for the Empty Application Example

* for ModusToolbox.

*

* Related Document: See README.md

*

*

*******************************************************************************

* Copyright 2021-2024, Cypress Semiconductor Corporation (an Infineon company) or

* an affiliate of Cypress Semiconductor Corporation. All rights reserved.

*

* This software, including source code, documentation and related

* materials ("Software") is owned by Cypress Semiconductor Corporation

* or one of its affiliates ("Cypress") and is protected by and subject to

* worldwide patent protection (United States and foreign),

* United States copyright laws and international treaty provisions.

* Therefore, you may use this Software only as provided in the license

* agreement accompanying the software package from which you

* obtained this Software ("EULA").

* If no EULA applies, Cypress hereby grants you a personal, non-exclusive,

* non-transferable license to copy, modify, and compile the Software

* source code solely for use in connection with Cypress's

* integrated circuit products. Any reproduction, modification, translation,

* compilation, or representation of this Software except as specified

* above is prohibited without the express written permission of Cypress.

*

* Disclaimer: THIS SOFTWARE IS PROVIDED AS-IS, WITH NO WARRANTY OF ANY KIND,

* EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, NONINFRINGEMENT, IMPLIED

* WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress

* reserves the right to make changes to the Software without notice. Cypress

* does not assume any liability arising out of the application or use of the

* Software or any product or circuit described in the Software. Cypress does

* not authorize its products for use in any products where a malfunction or

* failure of the Cypress product may reasonably be expected to result in

* significant property damage, injury or death ("High Risk Product"). By

* including Cypress's product in a High Risk Product, the manufacturer

* of such system or application assumes all risk of such use and in doing

* so agrees to indemnify Cypress against all liability.

*******************************************************************************/

/*******************************************************************************

* Header Files

*******************************************************************************/

#if defined (CY_USING_HAL)

#include "cyhal.h"

#endif

#include "cybsp.h"

#include "wave.h"

/******************************************************************************

* Macros

*******************************************************************************/

#define RXBUF_SIZE 60000

#define MI2C_TIMEOUT_MS 10u /* in ms */

#define MCLK_CODEC_DELAY_MS 10u /* in ms */

#define MCLK_FREQ_HZ 16083000u /* in Hz */

#define MCLK_DUTY_CYCLE 50.0f /* in % */

#define USB_CLK_RESET_HZ 100000 /* in Hz */

#define PLL_TIMEOUT_US 12000u /* in us */

#define PLL_FREQ_FOR_48KHZ 55296000 /* in Hz */

#define PLL_FREQ_FOR_44KHZ 50803200 /* in Hz */

#define MCLK_PIN P6_4

#define AUDIO_SYS_CLOCK_HZ 98000000u /* in Hz (Ideally 98.304 MHz) */

#define HFCLK1_CLK_DIVIDER 4u

/*******************************************************************************

* Global Variables

*******************************************************************************/

cyhal_i2s_t i2s;

cyhal_clock_t audio_clock;

cyhal_pwm_t mclk_pwm;

cyhal_clock_t audio_clock;

cyhal_clock_t pll_clock;

cyhal_clock_t fll_clock;

cyhal_clock_t system_clock;

const cyhal_i2s_pins_t i2s_tx_pins = {

.sck = P5_1,

.ws = P5_2,

.data = P5_3,

.mclk = P6_4,

};

const cyhal_i2s_config_t i2s_config = {

.is_tx_slave = false, /* TX is Master */

.is_rx_slave = false, /* RX is Master */

.mclk_hz = 11289600, /* External MCLK not used */

.channel_length = 16, /* In bits */

.word_length = 16, /* In bits */

.sample_rate_hz = 8000, /* In Hz */

};

/*******************************************************************************

* Function Prototypes

*******************************************************************************/

void i2s_isr_handler(void *arg, cyhal_i2s_event_t event);

/*******************************************************************************

* Function Definitions

*******************************************************************************/

/*******************************************************************************

* Function Name: main

*********************************************************************************

* Summary:

* This is the main function for CPU. It...

* 1.

* 2.

*

* Parameters:

* void

*

* Return:

* int

*

*******************************************************************************/

int main(void)

{

cy_rslt_t result;

#if defined (CY_DEVICE_SECURE) && defined (CY_USING_HAL)

cyhal_wdt_t wdt_obj;

/* Clear watchdog timer so that it doesn't trigger a reset */

result = cyhal_wdt_init(&wdt_obj, cyhal_wdt_get_max_timeout_ms());

CY_ASSERT(CY_RSLT_SUCCESS == result);

cyhal_wdt_free(&wdt_obj);

#endif

/* Initialize the device and board peripherals */

result = cybsp_init();

/* Board init failed. Stop program execution */

if (result != CY_RSLT_SUCCESS)

{

CY_ASSERT(0);

}

/* Enable global interrupts */

__enable_irq();

/* Initialize the User LED */

cyhal_gpio_init(CYBSP_USER_LED2, CYHAL_GPIO_DIR_OUTPUT, CYHAL_GPIO_DRIVE_STRONG, CYBSP_LED_STATE_OFF);

cyhal_gpio_init(CYBSP_USER_LED, CYHAL_GPIO_DIR_OUTPUT, CYHAL_GPIO_DRIVE_STRONG, CYBSP_LED_STATE_OFF);

// Synchronise MCLK

cyhal_gpio_init(MCLK_PIN,CYHAL_GPIO_DIR_INPUT,CYHAL_GPIO_DRIVE_NONE,true);

cyhal_gpio_read(MCLK_PIN);

/* Initialize the I2S */

cyhal_i2s_init(&i2s, &i2s_tx_pins, NULL, &i2s_config, NULL);

cyhal_i2s_register_callback(&i2s, i2s_isr_handler, NULL);

cyhal_i2s_enable_event(&i2s, CYHAL_I2S_ASYNC_TX_COMPLETE, CYHAL_ISR_PRIORITY_DEFAULT, true);

/* Start the I2S TX */

cyhal_i2s_start_tx(&i2s);

/* If not transmitting, initiate a transfer */

cyhal_i2s_write_async(&i2s, wave_data, WAVE_SIZE);

/* Turn ON LED to show a transmission */

cyhal_gpio_write(CYBSP_USER_LED2, CYBSP_LED_STATE_ON);

for (;;)

{

cyhal_system_delay_ms(10);

}

}

/*******************************************************************************

* Function Name: i2s_isr_handler

********************************************************************************

* Summary:

* I2S ISR handler. Stop the I2S TX and turn OFF the User LED.

*

* Parameters:

* arg: not used

* event: event that occurred

*

*******************************************************************************/

void i2s_isr_handler(void *arg, cyhal_i2s_event_t event)

{

(void) arg;

(void) event;

/* Stop the I2S TX */

cyhal_i2s_stop_tx(&i2s);

/* Turn off the LED */

cyhal_gpio_write(CYBSP_USER_LED, CYBSP_LED_STATE_OFF);

}

/* [] END OF FILE */

16 bits per each WCLK.

16 bits per each WCLK.