Other Parts Discussed in Thread: DIX9211

Tool/software:

Hello,

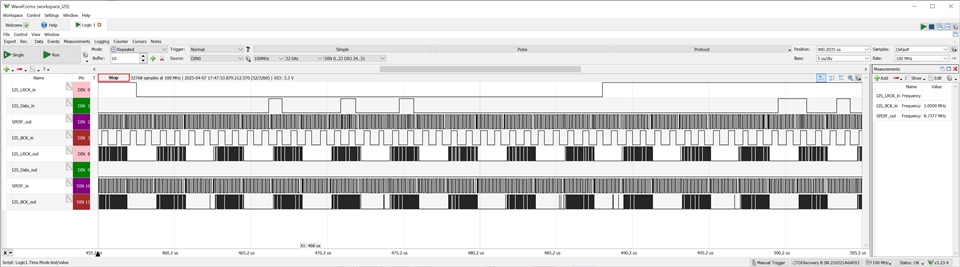

Not sure that parameters of input digital audio I2S are correct, but it seems that PCM9211 fails to convert it to S/PDIF: 0V ... instead of audiostream.

Here is my setup:

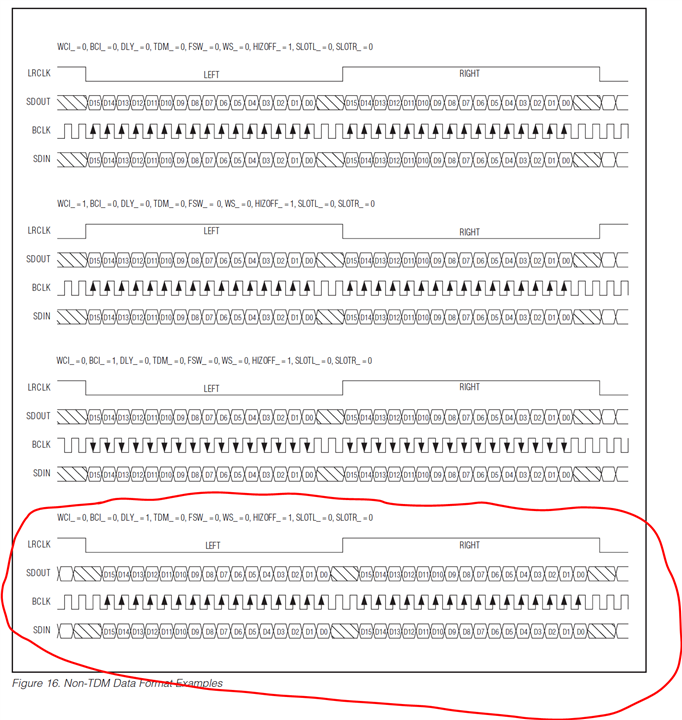

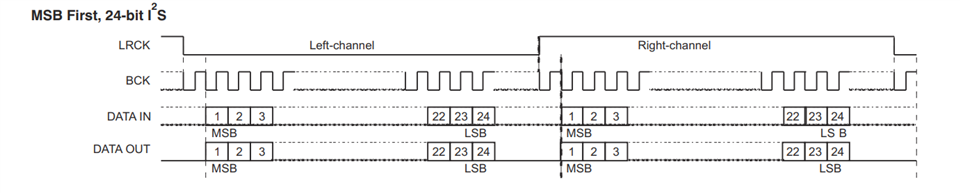

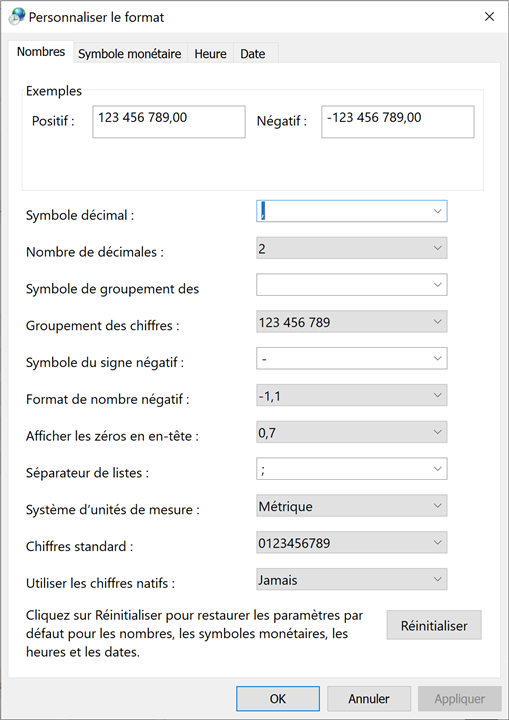

1. I2S parameters (configigured at the device that provides I2S):

- LRCLK frequency: 48kHz

- BCLK frequency: 48 x LRCLK frequency (i.e. 2.304 MHz)

- word size: 18 bits

2. I2S is applied to the MPIO_C port of PCM9211:

- BCLK --> MPIO_C1

- LRCLK --> MPIO_C2

- DATA --> MPIO_C3

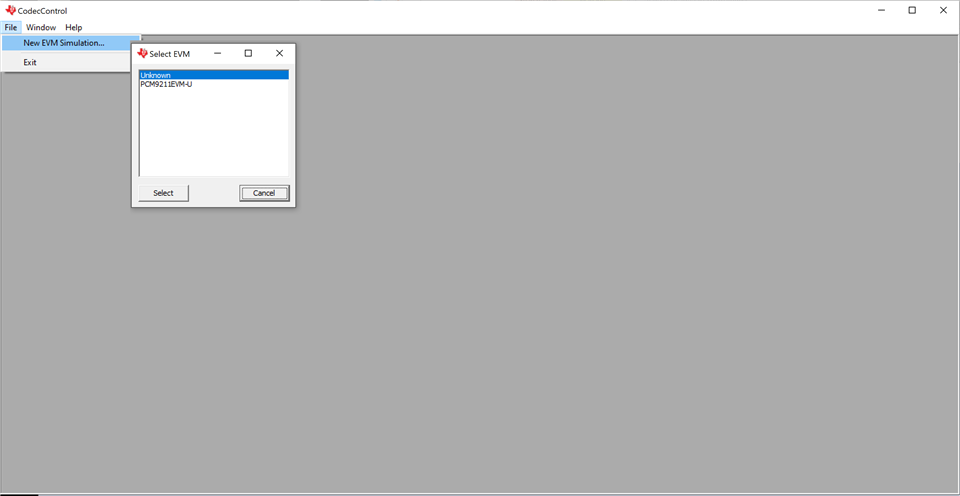

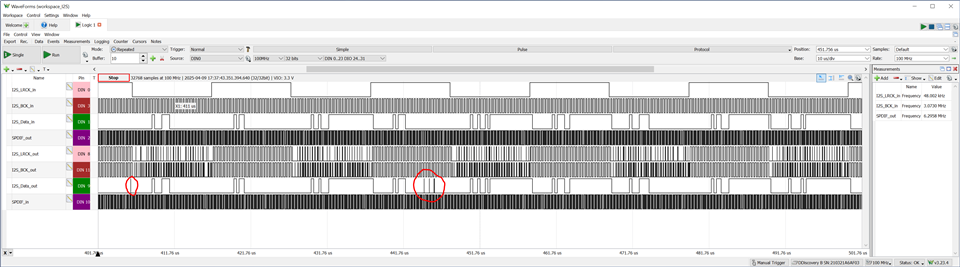

3. PCM9211 is configured as follows:

- Reg 0x6F: 0x05 ... enables DIT Standalone Mode

- Reg 0x24: 0x14 ... set master clock XMCKO as XTI/2, i.e. 12.288 MHz; Enable Output

- Reg 0x78: 0xCD ... route DIT Output (TXOUT) to MPO0 and XMCKO to MPO1

What is wrong with my setup ?

Thanks in advance

Pavel.