Other Parts Discussed in Thread: TAS2770

Tool/software:

Hello,

I have a custom design where an MCU drives TAS2780. The audio data is hardcoded in the firmware ( this is for test purpose). The SAI settings are as below

Sampling rate 48k

Bitwidth: 16

Channel/mode : Stereo

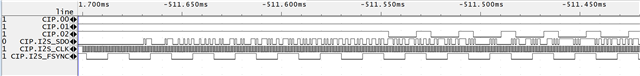

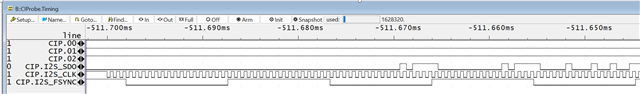

Attached are the waveforms of I2S CLK, DATA and FSYNC. Can you check if TAS2780 can accept this format ?

I also decoded and plotted the complete I2S data & i could see a sine wave as I had expected.

Coming to the TAS side of things, TAS seems to be completely silent. Below are the custom settings that i had applied to TAS2780

0x00, 0x00, //access page 0

0x0A, 0x32, //Stereo down mix, word slot and time slot 16/32 bits.

0x60, 0x00, //sclk and fsync ratio :16

0x08, 0x19 //disable auto rate detection

Attached is the full TAS2780 initialization code that I did.

My questions are:

1. Will tas2780 accept classic I2S stereo stream? FYI: I2C address of the device is 0x70

2. What are the additional settings needed for TAS2780 to accept the above datastream

3. Is my initialization sequence correct ? Each row in the array ( of TAS2780_init.h) is sent to TAS2780 as a separate I2S write transaction. First entry in the row is register address and last entry in the row is data.