Tool/software:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

Can you attach a more thorough description of what you are doing to configure your driver, what is your DTS file or any other commands used to get this error? Also, what are your input and output clocks to the codec? Can you make sure that you have an MCLK or BCLK into the device coming from your MCU? You may need to define the input/output clocks for this section of the driver to function as expected.

Best,

Mir

I downloaded the driver file here: www.ti.com.cn/.../TLV320AIC31XX-DRIVERS.

DTS:

i2c_4{

- clock-frequency = <400000>;

+ clock-frequency = <100000>;

}

+ tlv320aic3x: tlv320aic3x@1b {

+ #sound-dai-cells = <1>;

+ compatible = "ti,tlv320aic3x";

+ reg = <0x1b>;

+ reset-gpios = <&peri_port0 23 GPIO_ACTIVE_LOW>;

+ AVDD-supply = <&tlv3v3_fixed>;

+ IOVDD-supply = <&tlv1v8_fixed>;

+ DRVDD-supply = <&tlv3v3_fixed>;

+ DVDD-supply = <&tlv1v8_fixed>;

+ };

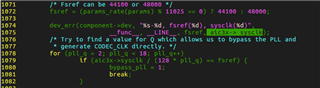

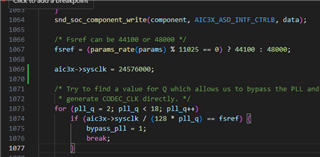

Through the log, I found that the value of aic3x->sysclk in the aic3x_hw_params() function is 0.

Hi,

What MCLK, BCLK, and WCLK are you providing or expecting from the device? How else are you configuring, or is the code you posted the only thing? Are you using ALSA? Sysclk is typically the internally generated output of the PLL, and if you are having an error with establishing the PLL, then it makes sense for sysclk to be 0.

Best,

Mir

It is the ALSA architecture. In the DTS, the configuration of mclk_set is <24576000>.

snd2_tlv: snd2_tlv {

status = "okay";

model = "s100snd2-tlv320";

compatible = "hobot, s100-snd-ac-fdx-master";

i2s_mode = <1>;/*1:i2s mode; 7:dsp_a mode*/

work_mode = <1>;/*0:hal-duplex; 1:full-duplex*/

channel_max = <2>;

mclk_set = <24576000>;

dai-link@0 {

dai-format = "i2s"; //"i2s"/"dsp_a"

link-name = "j6dailink0";

cpu {

sound-dai = <&i2s0 0>;

};

codec {

sound-dai = <&tlv320aic3x 0>;

};

};

dai-link@1 {

dai-format = "i2s";

link-name = "j6dailink1";

cpu {

sound-dai = <&i2s0 1>;

};

codec {

sound-dai = <&tlv320aic3x 0>;

};

};

};

Hi Wenzel,

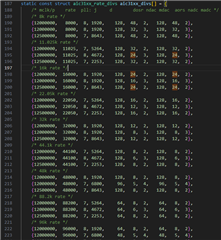

The 24576000 MCLK rate does not exist in the driver's default aic31xx_divs section, so I would recommend adding a new line in the driver to correspond to your PLL divider needs. What sample rate and bit depth are you using, so I can calculate the dividers for you? Are you using the device in I2S target or controller mode (slave or master mode)?

Best,

Mir

The codec is used in slave mode. Do we still need to configure the codec's clock in slave mode?

In addition, there is no aic31xxdiv [] in my driver file. The currently running driver file is tlv320aic3x.c, not tlv320aic31xx.c. Could you please tell me which is the correct driver program for the TLV320AIC3104 chip?

Hi,

Yes, sorry - aic3x.c is the correct driver. I assume your fs is 48k? You still need the PLL enabled to generate internal clocks, and it looks like the driver expects to be told fsref and potentially the MCLK rate by your dts file. Are you providing the 24576000Hz clock at the MCLK pin, and are you providing the 48k WCLK and the BCLK?

You may need to set the sysclk in the driver code itself, like this:

Best

Mir