Other Parts Discussed in Thread: PUREPATHSTUDIO

Tool/software:

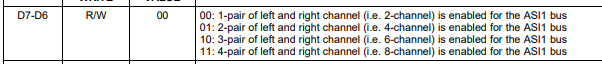

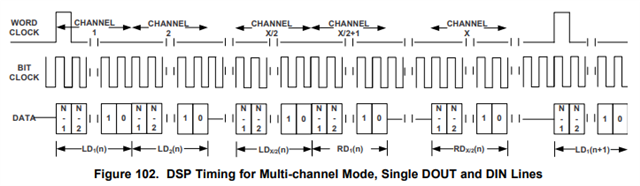

Just designed a system with the aic3268. This system requires to mux two 32bit mono pcm buses from ASI2 and ASI3 to a 8-channel TDM bus on ASI1. Also in opposite direction. So two channels from TDM on the Din on ASI1 to the DOUT of ASI2 and ASI3.

Found out that for this configuration I need to program one or both mini-dsp's. So in the meantime I have purepathstudio running and the aic3268 is listed under frameworks.

However I don't have an usb-i2c programmer with the TAS1020B or an evaluation board. And it seems like the evaluation board is obsolete.

So my question is: How am I be able to program the mini-dsp's on the aic3268?

I do have a EVAL-ADUSB2EBUZ available(also usb-i2c). Furthermore I noticed the TTK USBtoI2X dongle on: https://e2e.ti.com/support/audio-group/audio/f/audio-forum/299026/ttk-reference-designs-for-audio-converters

Can I order such a dongle anywhere? Could I design it myself? And I think the TAS1020B needs firmware for that, where could I find that?

Sorry for that much questions, but I would like to know if it's even possible what I am trying to accomplish.