Hi,

I have a design centered around an AM1808 which is laid out using McASP0 to interface to a TLV320AIC3100. Up to this point I've been able to use the existing davinci-evm.c and davinci-mcasp.c SoC modules with slight modifications to get data out of the AM1808 using aplay to playback a wave file. I've based my own board file off of the existing board-da850-evm.c file which registers the davinci-evm.c, davinci-mcasp.c and tlv320aic3x.c modules such that aplay sees a sound card. I've been modifying the tlv320aic3x.c driver to control my tlv320aic3100 and have come to a point where I believe I have all registers set appropriately for playback out of both the speaker and headphone outputs. I haven't gotten to the ADC side of things yet as I'm trying to get DAC outputs going first.

The issue I'm having with the codec setup is that the DAC flag register (page 0 register 37) only shows the Left channel DAC powered on while all the control registers indicate the left and right channel DACs, speaker amp driver and the right and left channel headphone drivers are all powered on.

CLASSD_SPEAKER_AMP(P1/R32): 0x86 Bit 7 indicates class-D speaker amp powered up

DAC_CHN_REG(P0/R63): 0xd4 Bits 6 and 8 indicate right and left DACs powered up

HEADPHONE_DRIVER(P1/R31): 0xd4 Bits 6 and 7 indicate right and left head phone drivers powered up

DAC_FLAG_1(P0/R37): 0x80 Only bit 7 is set indicating left DAC is powered up.

I'm not sure if I'm missing something or not but I'm guessing I need to see everything powered up in the DAC flag register before I'll get any audio out. Is this a safe assumption? Is there a sequence of events that needs to take place which isn't outlined in the datasheet that I might need to follow? I am performing both a hard and soft reset when the driver is probed.

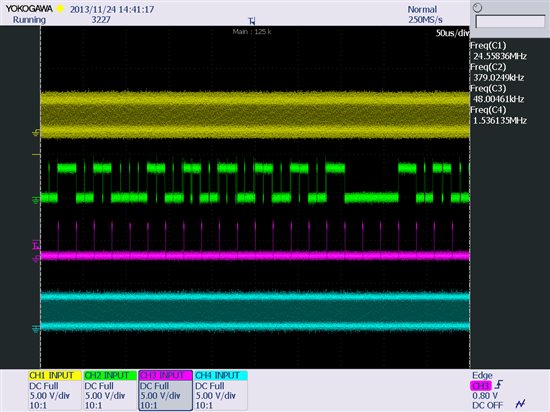

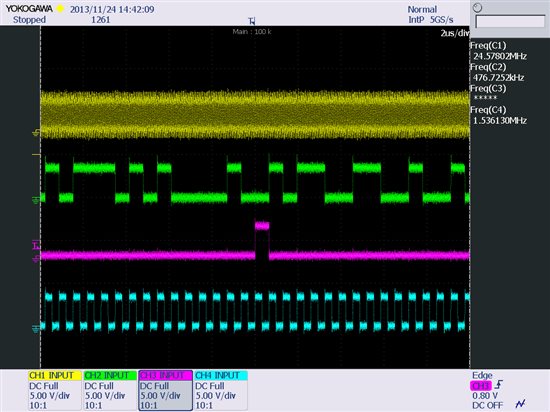

Below are all of my register values read back that I've written to in addition to some read only registers. I'm using the codec as a frame and master clock slave. The master clock rate is 24.576MHz, bit clock rate is 1.536MHz and the sampling frequency is 48kHz.

AIC3X_RESET(P0/R1): 0x0

OT_FLAG(P0/R3): 0x2

INTERFACE_SET_REG_1(P0/R27): 0x40

INTERFACE_SET_REG_2(P0/R29): 0x0

CLK_REG_2(P0/R5): 0x81

CLK_REG_3(P0/R6): 0x1

CLK_REG_4(P0/R7): 0x0

CLK_REG_5(P0/R8): 0x0

NADC_CLK_REG(P0/R18): 0x82

MADC_CLK_REG(P0/R19): 0x81

ADC_OSR_REG(P0/R19): 0x20

BCLK_N_VAL(P0/R30): 0x18

DOUT_CTRL(P0/R53): 0x2

ADC_FLAG(P0/R36): 0x80

NDAC_CLK_REG(P0/R11): 0x82

MDAC_CLK_REG(P0/R12): 0x81

DAC_OSR_MSB(P0/R13): 0x0

DAC_OSR_LSB(P0/R14): 0x20

DAC_CHN_REG(P0/R63): 0xd4

DIN_CTL(P0/R54): 0x2

DAC_MUTE_CTRL_REG(P0/R64): 0x0

AIC3100_LDAC_VOL(P0/R65): 0x0

AIC3100_RDAC_VOL(P0/R66): 0x0

DAC_FLAG_1(P0/R37): 0x80

DAC_FLAG_2(P0/R38): 0x80

OVERFLOW_FLAG(P0/R39): 0x0

VOL_MICDECT_ADC(P0/R116): 0x80

VOL_MICDECT_GAIN(P0/R117): 0x0

L_ANLOG_VOL_2_SPL(P1/R38): 0x80

DAC_MIX_CTRL(P1/R35): 0x44

CLASSD_SPEAKER_AMP(P1/R32): 0x86

SPK_DRIVER(P1/R42): 0x14

HEADPHONE_DRIVER(P1/R31): 0xd4

L_ANLOG_VOL_2_HPL(P1/R36): 0x80

R_ANLOG_VOL_2_HPR(P1/R37): 0x80

HPL_DRIVER(P1/R40): 0x36

HPR_DRIVER(P1/R41): 0x36

ADC_PRB_SEL_REG(P0/R61): 0x4

MIC_PGA(P1/R47): 0x0

MIC_GAIN(P1/R48): 0x30

AIC3100_MICBIAS_CTRL(P1/R46): 0x9

ADC_FGA(P0/R82): 0x0

I did see the post "Linux device drivers for AIC31xx/DAC31xx/AIC325x/AIC320x/AIC326x/AIC321x" http://e2e.ti.com/support/data_converters/audio_converters/f/64/t/266169.aspx and cloned the git project but was unable to find any code, specifically in sound/soc/codecs/, that pertained to the 3100.

I also began following the instructions but I seem to be missing "Support Texas Instruments AIC31XXX" and "Support Texas Instruments AIC3XXX platform with I2C" under Device drivers -> Multifunction device drivers in the kernel menuconfig.

Does an ALSA SoC driver currently exist for the TLV320AIC3100?