Dear team,

I am making a script of AIC3254 AEC(Echo cancellation) with 8kHz sampling rate for Samsung smart home project needs AEC for refrigerator...

and get the attached codec/mDSP script and get the right operation...

However, Samsung is asking the bypass of AEC and non audio processing with 48kHz sampling rate under smallest modified setting from AEC script..

Actually, I got this below setting to have the bypass mode but we need full AEC script with RESET again whenever we switch AEC and non AEC each other..

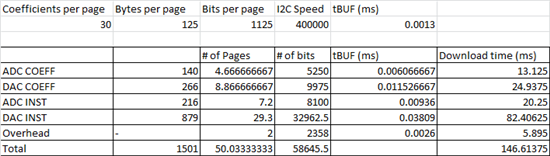

it take more than 1sec time with 400kHz I2C speed to write each initialization about AEC(8kHz PLL and mDSP processing) and non AEC(48kHz and mDSP bypass) whenever mode change..

Samsung is asking <100mS to chage the mode!!!!

Please help me to find out the way to swith the two mode with minimum script..

- 48kHz normal processing (only codec setting + PRB1 processing )

- 8kHz AEC processing ( Codec setting + PLL + mDSP processing on)

Thanks and best regards,

JY- Samsung account.

------------------- 48kHz non audio processing ----------------------------------------------------------------------------

# High Performance Stereo Playback

# ---------------------------------------------

# PowerTune mode PTM_P3 is used for high

# performance 16-bit audio.

#

# Audio is routed to both headphone and

# line outputs.

###############################################

###############################################

# Software Reset

###############################################

#

# Select Page 0

w 30 00 00

#

# Initialize the device through software reset

w 30 01 01

#

###############################################

###############################################

# Clock Settings

# The codec receives: MCLK = 12.288 MHz,

# BLCK = 3 MHz, WCLK = 48 kHz

###############################################

#

# Select Page 0

w 30 00 00

#

# NDAC = 1, MDAC = 2

w 30 0b 81 82

#

###############################################

###############################################

# Signal Processing Settings

###############################################

#

# Select Page 0

w 30 00 00

#

# Set the DAC Mode to PRB_P1

w 30 3c 01

#

###############################################

###############################################

# Configure Power Supplies

###############################################

#

# Select Page 1

w 30 00 01

#

# Power up AVDD LDO

w 30 02 A9

#

# Disable weak AVDD in presence of external

# AVDD supply

w 30 01 08

#

# Enable Master Analog Power Control

# Power up AVDD LDO

w 30 02 A1

#

# Set the input power-up time to 3.1ms (for ADC)

w 30 47 32

#

# Set the REF charging time to 40ms

w 30 7b 01

#

###############################################

###############################################

# Playback Setup

###############################################

#

# Select Page 1

w 30 00 01

#

# De-pop: 16 time constants, 6k resistance

w 30 14 35

#

# Route LDAC/RDAC to HPL/HPR

w 30 0c 08 08

#

# Power up HPL/HPR and LOL/LOR drivers

w 30 09 3C

#

# Unmute HPL/HPR driver, 0dB Gain

w 30 10 00 00

#

# Select Page 0

w 30 00 00

#

# DAC => 0dB

w 30 41 00 00

#

# Power up LDAC/RDAC

w 30 3f d6

#

# Unmute LDAC/RDAC

w 30 40 00

#

###############################################

###############################################

# High Performance Stereo Recording

# ---------------------------------------------

# PowerTune mode PTM_R4 is used for high

# performance 16-bit audio.

#

# IN2L/R is routed to the LADC/RADC in a

# single-ended manner.

###############################################

###############################################

# Clock Settings

# ---------------------------------------------

# The codec receives: MCLK = 12.288 MHz,

# BLCK = 3 MHz, WCLK = 48 kHz

###############################################

#

# Select Page 0

w 30 00 00

#

# NADC = 1, MADC = 2

w 30 12 81 82

#

###############################################

###############################################

# Signal Processing Settings

###############################################

#

# Select Page 0

w 30 00 00

#

# Set the ADC Mode to PRB_P1

w 30 3d 01

#

###############################################

###############################################

# Recording Setup

###############################################

#

# Select Page 1

w 30 00 01

# Mic Bias on

w 30 33 60

# Route IN3L to LEFT_P with 20K input impedance

w 30 34 08

#

# Route CM1L to LEFT_M with 20K input impedance

w 30 36 80

#

# Route IN3R to RIGHT_P with 20K input impedance

w 30 37 08

#

# Route CM1R to RIGHT_M with 20K input impedance

w 30 39 80

#

# Unmute Left MICPGA, Gain selection of 20dB to make channel gain 0dB

# Register of 6dB with input impedance of 20K => Channel Gain of 0dB

w 30 3b 26

#

# Unmute Right MICPGA, Gain selection of 20dB to make channel gain 0dB

# Register of 6dB with input impedance of 20K => Channel Gain of 0dB

w 30 3c 26

#

# Select Page 0

w 30 00 00

#

# Power up LADC/RADC

w 30 51 c0

#

# Unmute LADC/RADC

w 30 52 00

#

###############################################