Hi.

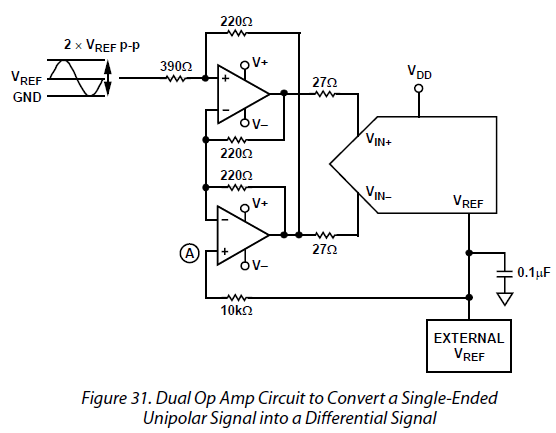

I am reading data from PCM4220 through TMS320C6745.

I have the next configuration:

1) PCM4220

- Master mode

- Double Speed mode

- Classic filter response

- SUB0 = 0 and SUB1 = 0: Sub-frame 0

- OWL0 = 0 and OWL1 = 0: 24-bits

- FMT0 = 1 and FMT1 = 0: I2S

Audio serial port bit clock - 6,14407 MHz

Audio serial port left/right word clock - 96 KHz

Master clock - 12,2881 MHz

2) DSP

Codec connected through McASP.

Master clock - 24,576 MHz (Is it correctly ?)

My problem:

1) I connect VINL-, VINL+,VINR-, VINR+ pin to the ground.

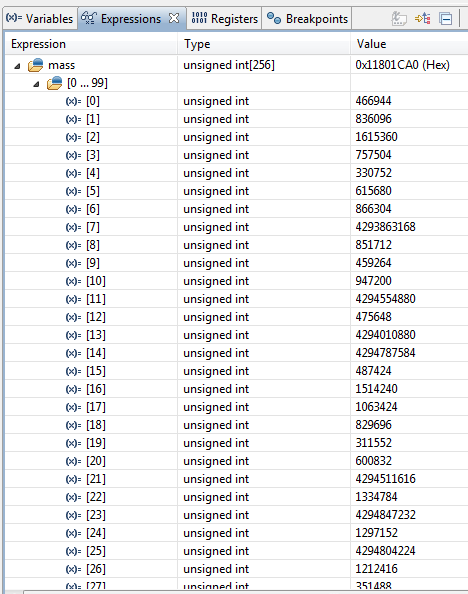

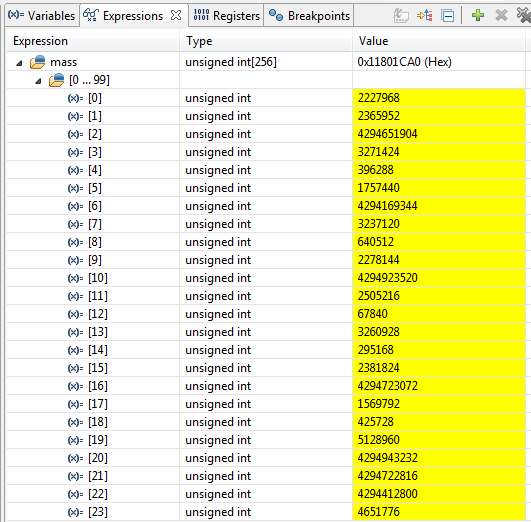

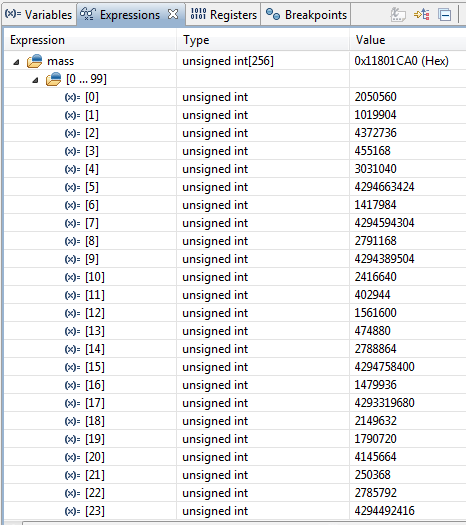

But my received DATA in the buffer are the next:

I don't understand why values do not match:

866304 and 4293863168

4293863168 and 851712

851712 and 459264

etc.

Values should strive to zero, but I have values 4293863168. Why?

Your help will save me a lot of time.

Thanks.