Part Number: PCM9211

Other Parts Discussed in Thread: CDCLVC1102, SRC4192

Hello,

I have a question regarding I2S audio routing within a design around PCM9211.

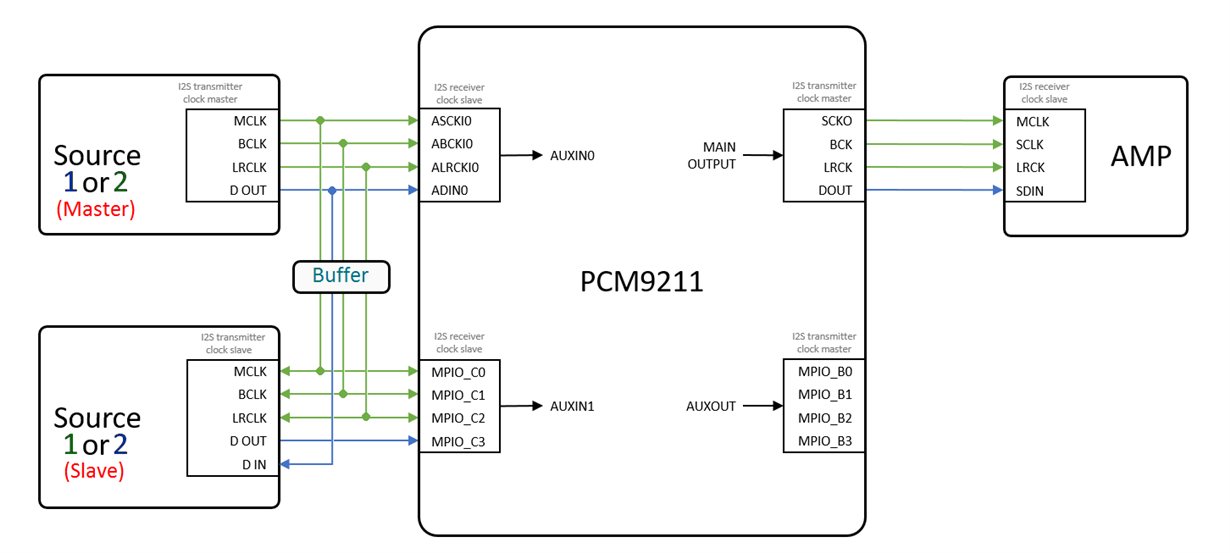

The PCM is used as multiplexer here.

There is one output device (an I2S input class D amp) on the PCM's main output.

There are two input devices: one on the AUXIN0 port, another on the AUXIN1 port.

The output device is a I2S receiver in clock slave mode.

The input devices are I2S transmitters in clock master mode.

From the PCM9211's datasheet I understand this setup is ideal, right?

Now, the second source device, has also an I2S data input which I want to use. There are however no seperate clock lines for this input, the same as for it's output must be used.

My goal is to make a route possible for audio comming from source 1 to the source 2 device input.

Since the PCM has multiple outputs (AUXOUT), which can be independent from the main output, I was thinking to use the PCM MUX for this as well.

However: I read in it's datasheet AUXOUT can only operate in I2S clock master mode.

Problem: The source 2 device is already master...

Is there something I missed out and is there a way to use AUXOUT or another output to accomplish this audio route?

If no: what is the best alternative?

The PCM9211 is tremendously versatile, so I believe it's possible in some way, but I'm not sure.