Other Parts Discussed in Thread: CDCM6208, CDCM6208V1

Hello,

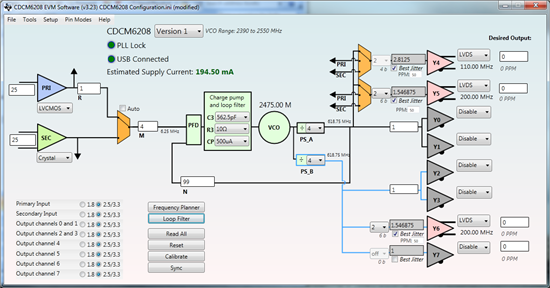

We are using CDCM6208 to generate below frequencies

1. 200MHz @ Y5

2. 200MHz @ Y6

3. 110MHz @ Y4

All are set as LVDS outputs. We feed 25MHz TCXO as the Primary Reference clock.

We have simulated for these frequencies in EVM software and we got the register values which are attached as text file with this post. With these values, in Simulation software, we are able to get accurate output frequencies. However when we load the registers on our custom board, the output frequencies are 116MHz @ Y4 and 208MHz @ Y5 & Y6.

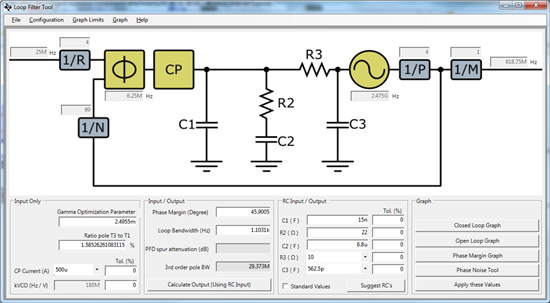

Why is this deviation? We have designed Loop Filter for 1KHz (The Schematics is attached with the post)