Other Parts Discussed in Thread: ADC12DL3200

Dear Sirs,

in my design I use four ADC12DL3200s. The ADC clocks are generated with the following chain:

- source LMX2594;

- buffer 1:4 HMC987;

- switch NB7V72MMNG (one for each ADC12DL3200);

- div2 NB7L32M the output is connected to the ADC12DL3200 clock input.

The switch NB7V72MMNG selects the clock source between the internal source (LMX2594+HMC987)

or an external clock.

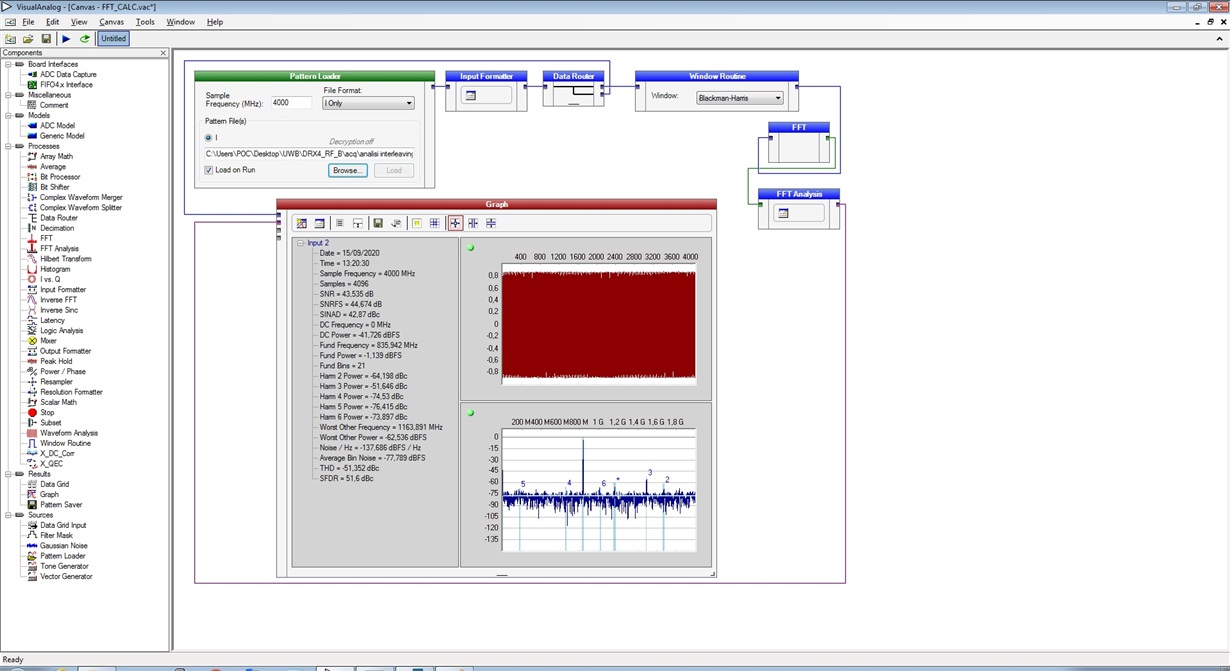

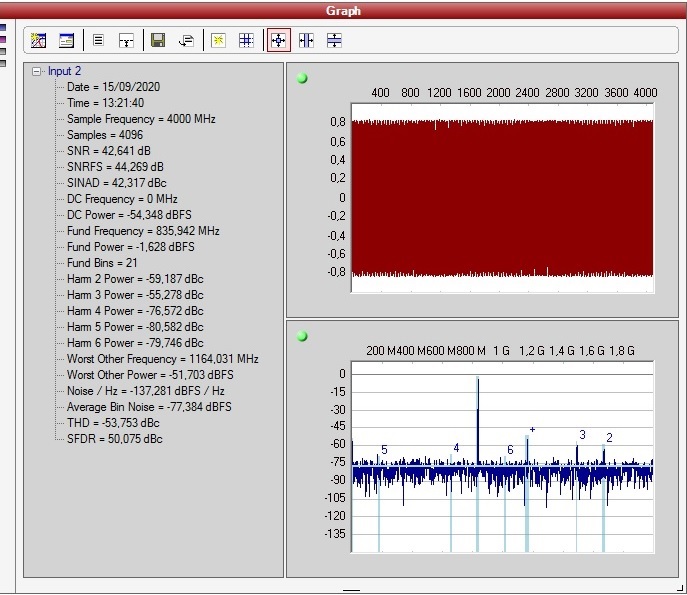

In this configuration, when I generate a 4 GHz clock and then select with the NNB7V72MMNG

the internal source, the ADC12DL3200s work correctly but they generate also an interleaving spurious

(clock or Gain). Usually this spurious have a power between the -45 and -60 dBFs.

When I select with the NB7V72MMNG an external source generated by a RF instrument

(always 4 GHz), the interleaving spurious there aren' t.

If I re-calibrate the PLL this interleaving spurious can change the values -45 to -60 dBFs (also

If I re-power on the board), while when I re-calibrate the ADC, the spurious power are the same.

One of the possible source of this spurious is the interconnection between the PLL LMX2594 and

and the HMC987. The two components have an A.C. coupling, the LMX2594 have a 50 Ohm to 3.3

and the HMC987 input has an internal termination: PECL termination and 50 Ohm.

Do you have any suggestions about the origin of the interleaving spurious?

Could you help me to understand why the ADC12DL3200 generates the interleaving spurious?

Are there specific conditions to have these types of spurious (for example the clock is non symmetric

or the duty cycle is not 50%)

Do you think that the LMX2594 work correctly with the HMC987?

Thanks in advance.

Best Regards.