Part Number: LMK04616

Dear team

We plan to use the LMK04616 in PLL2 only mode, with OSCin, for both ZDM and pure buffer mode. And we have some confuse as below:

1. In ZDM mode, the feedback channel is CH7/8 or CH 6/9?

2. In ZDM mode, and also need to sync all the output divider, will our device support?

3. In ZDM mode, the phase error between input and feedback channel?

4. OSCout will always have same frequency as OSCin in any condition?

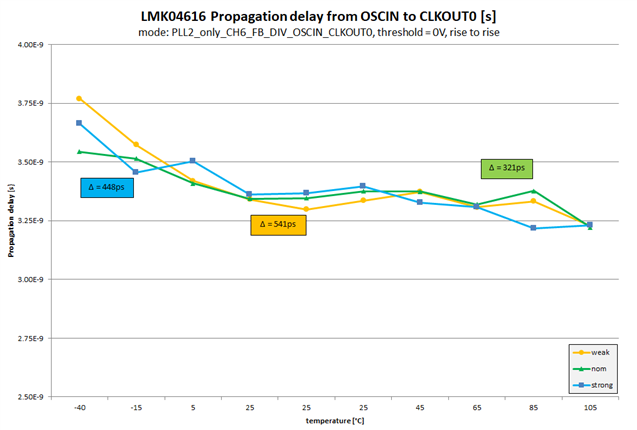

5. In Buffer mode, the OSC in to Clkout propagation delay, Min and Max value?

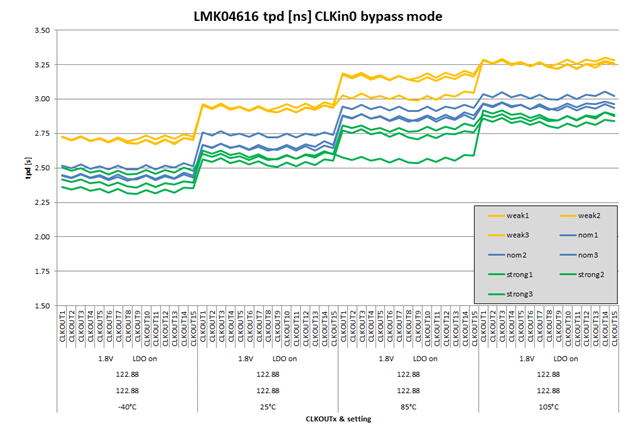

6. In Buffer mode, the part to part skew, Min and Max Value?

Thanks

Jun Shen