I see from the documentation that: "An extended assertion of a logic HIGH at the DELAY/M_DRV pin will turn on the MOSFET for a time longer than the programmed time interval. DONE signals received while the DELAY/M_DRV is HIGH are ignored. If the DRV is already LOW (MOSFET ON) the manual power ON is ignored."

I am making remote blinds. The microcontroller on the blinds needs to power up once per three seconds to look for a radio signal. If it is present, then it needs to drive a motor and take actions for 10 seconds. Thus, I want the TPL5110 to power up the microcontroller once per three seconds, but if a signal is present then I cant have the microcontroller reset when the TPL5110 timer elapses in three seconds since the microcontroller needs to take actions for 10 seconds.

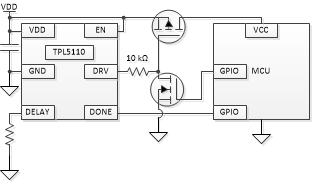

Would the following work? I power the microcontroller off the DRV pin. I set the resistance on the TPL DELAY pin for 3 seconds. Every 3 seconds the TPL5110 turns the microcontroller on. While the microcontroller is on, if it sees the radio signal, then it will use one of its GPIOs to bring the DELAY pin HIGH and keep it high until the microcontroller finishes its ten seconds of tasks. Then the microcontroller changes that GPIO output to LOW (or changes it to a floating input) and uses another GPIO to bring the DONE pin HIGH to get the TPL5110 to cut power.