Other Parts Discussed in Thread: LMK03328

Hello,

I am working on a brand new design for the TMS320C6678ACYP. Pursuant to a suggestion in an earlier e2e dialogue, I have chosen to use the LMK03318 Clock Generator to provide the clocks for the DSP. It turns out that ROM Option 45 will do everything I need: 100MHz for the CORECLK on Output 0, 100MHz for the DDRCLK on Output 2, and 250MHz on Output 4 for the SRIOSGMIICLK. I have the HW_SW_CTRL pin tied to 3.3V. I have six questions:

1) Since I am not using the rest of the outputs, do I need to provide the filter networks for all of the VDDO pins, or can I simply connect VDDO_5, VDDO_6, and VDDO_7 to 1.8V directly?

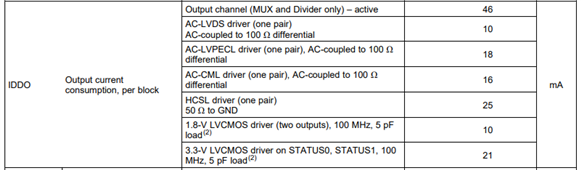

2) How much power could I save if I developed a custom program for our application and disabled the outputs for all of the unused clocks?

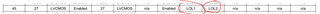

3) With ROM Option 45 what is driven onto the STATUS0 and STATUS1 pins?

4) Since I’m only using the 25MHz crystal connected to the SECREF_P and SECREF_N pins, and have no other clock sources, what should I connect to the PRIREF_P and PRIREF_N pins?

5) Is VCO calibration as described on page 42 of the datasheet necessary to meet the phase noise or any of the other requirements of the TMS320C6678ACYP?

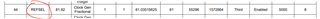

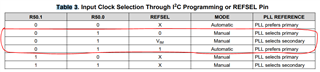

6) I have read page 33 of the datasheet, but I don’t know what R50.1 and R50.0 are set to when using ROM Option 45. I have tied the REFSEL pin to VIM. With ROM Option 45 will this force the device to use the secondary crystal input pins manually or will the device automatically select the crystal by itself?

Best Regards,

Larry