Other Parts Discussed in Thread: LMX2594

I need help with my LMK04208 circuit. I cannot get PLL1_LOCK.

I designed my own PCB based on the Xilinx ZCU111 and the XCZU28DR RFSOC. My LMK04208 circuit is almost identical the ZCU111 circuit with the exception of the TCXO and VCXO components. My VCXO is an Epson VG-4513CA 122.8800M-GFCT3 and my TCXO is a CTS 581L128X2ITT (12.8MHz HCMOS). The VCXO is connected differential and TCXO is connected single-ended AC coupled and CLK_IN0_N pin is connected to GND through a 0.1uF capacitor. CLK_IN1 is NC. I have been working on this circuit for weeks and the best that I can get out of the device is 6MHz out of CLKout0 and 1MHz out of CLKout1. Also, the register values that I write to the LMK04208 in 25ms intervals are almost identical to the ones used by the ZCU111 and they work on the ZCU111.

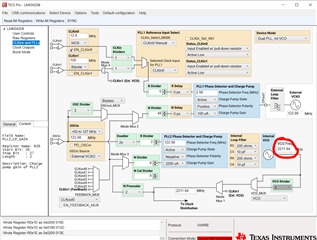

First, I know the SPI is working because I can read the values that I have written to the registers. I have also been using TICS as a guide which has helped me learn the device better. One concern that I have with my circuit is the TCXO. The output is a solid 12.8MHz but the output level was 3VPP. The output of the ZCU111 TCXO is about 2.2VPP. I then read in the datasheet that the maximum input to the CLK_IN0 pin is 2.4V. I have since added some attenuation (100ohms, 240ohms) and now the AC coupled output is 2VPP and there is also 1.6VDC bias tied to pin 28.

So is there a chance that my LMK04208 is damaged from the 3VPP input to pin 28? I have a LED tied to the LD pin and the only settings that make the LED illuminate from Table 49 LD_MUX are 12, 14, 15, 16 and 18. My goal is to get PLL1 and PLL2 DLD to activate the LED.

I have looked through the TI forums for guidance but could not find anything helpful. So could someone please tell me if there is a possibility that my excessive TCXO output could have damaged the LMK04208? Also, if you have any advice on setting this IC up with the simplest register settings in order for me to test the clock outputs, please let me know. Please advise. Thanks.