Hello,

My customer would like to use CDCM7005-SP as follows.

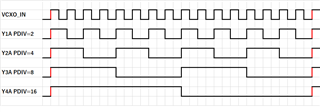

- VCXO_IN --> PDIV=/2 --> Y0A(LVPECL)

- VCXO_IN --> PDIV=/4 --> Y1A(LVPECL)

- VCXO_IN --> PDIV=/8 --> Y2A(LVPECL)

- VCXO_IN --> PDIV=/16 --> Y3A(LVPECL)

About this usage, they have some questions as follows.

Q1:

Y0A, Y1A, Y2A and Y3A rising edge phases are aligned once 16 VCXO_IN cycles as follows?

Or a reset is required to align them as follows?

Q2:

In Figure 11 of the datasheet, how much is the maximum tpd(LH), maximum tpd(HL), minimum tpd(LH) and minimum tpd(HL) for LVPECL output respectively?

Q3:

How much is the delay from deassertion of reset_ to YnA output first rising edge?

Best regards,

K.Hirano