Other Parts Discussed in Thread: LMK04832, LMK1D1204

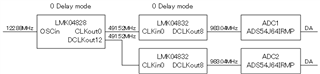

The data acquired by LMK04828 + LMK04832 + ADC (ADS54J64IRMP) are compared.

Even if the SPI is set after the power is turned on and off (the parameters are consistent each time and the parameters are consistent between the two devices), the phase of ADC2 with reference to ADC1 is basically the same phase difference. , There are some fluctuations.

I would like to know if this slight fluctuation is within the permissible range, but how should I consider it? (Jitter?, skew?)