Other Parts Discussed in Thread: LMX2572, LMK04828

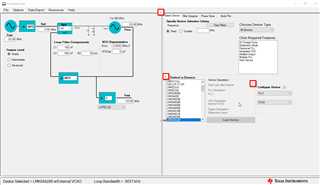

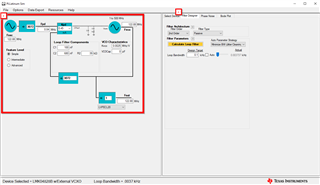

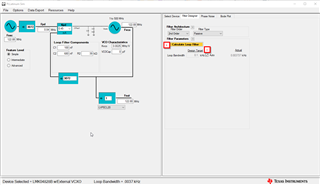

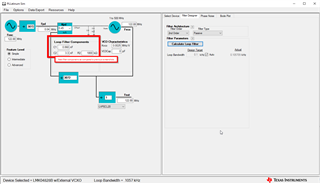

We are working with a LMK04828B board and TICSpro

We are trying to generate a 1 GHz clock using a 25 MHz input (CLKin1).

1. In our first configuration we use an AWG to generate the 25 MHz, in this case the CLKin1 is very low jitter, and we can see that the board locks to it (both PLL1 and PLL2 LEDs are ON). Monitoring on the scope we see that the 25 MHz and the 1 GHz are locked to each other.

2. In the second configuration, we use an electronic board to generate the 25 MHz (CLKin1). The jitter of the 25 MHz generated by our board is higher than when generated with an AWG. In this case we are unable to lock the 1 GHz to the CLKin1. The PLL1 LED is OFF, but the PLL2 LED is ON.

3. As a simple test, we also use a PLL+VCO model LMX2572 to generate 1GHz using the jittery 25 MHz: this configuration works without problem and the 1GHz generated clock is locket to the jittery 25 MHz input clock.

We expected the jitter cleaner feature of the LMK04828B to help it lock better. However, with the jittery 25 MHz, we could not find what settings combination would let the LMK04828B generate a 1 GHz locked to the 25 MHz CLKin1. Can you please explain why and help us debug it?

Kind regards