Other Parts Discussed in Thread: TLV170

Hi Team,

Can you please check the inquiry below?

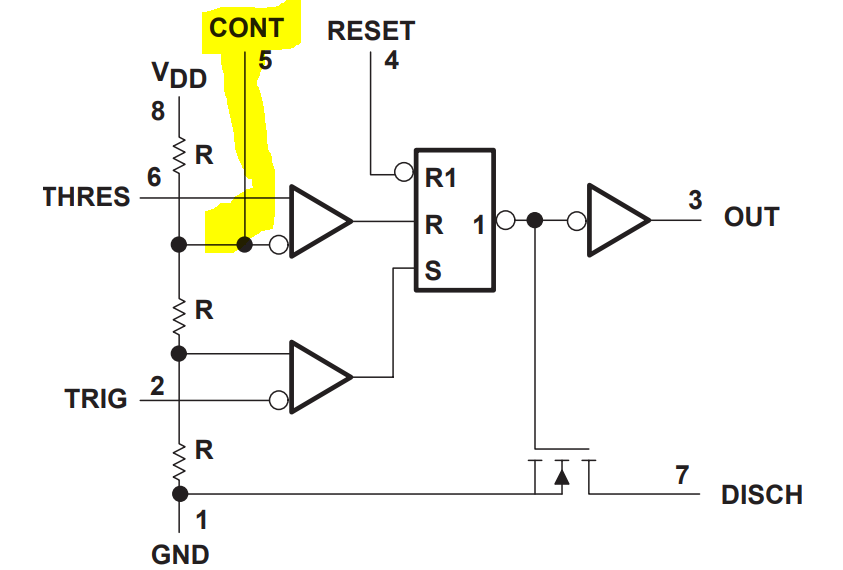

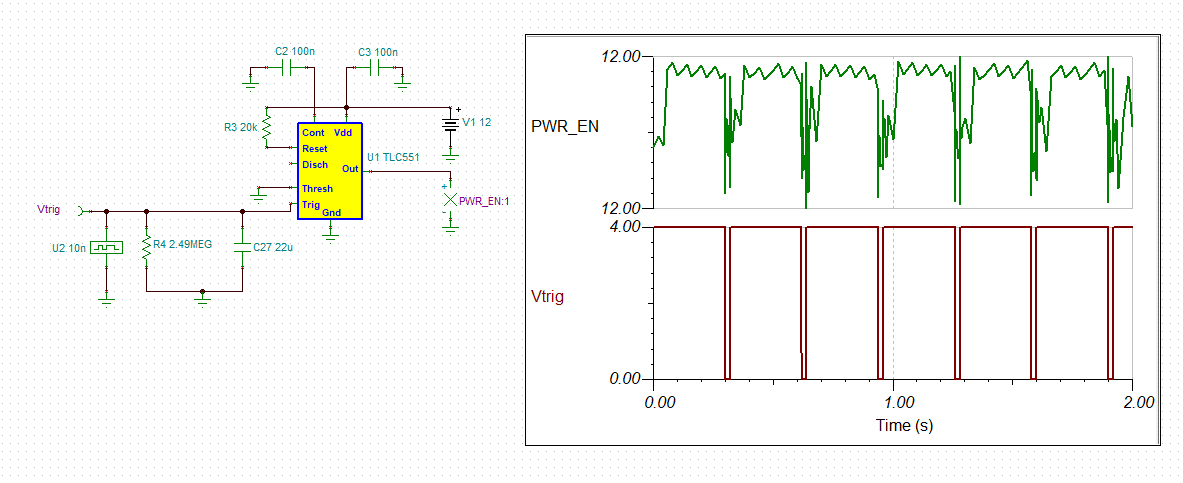

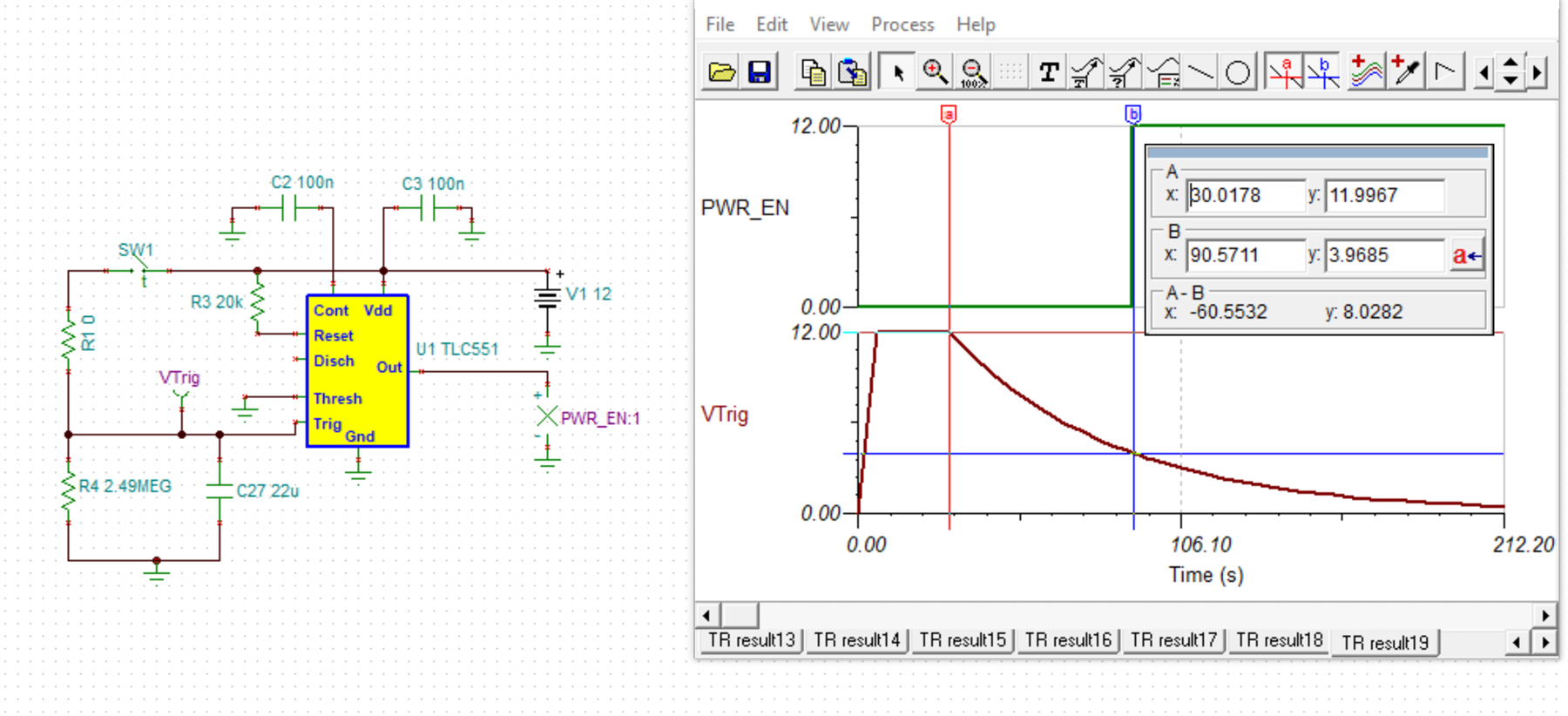

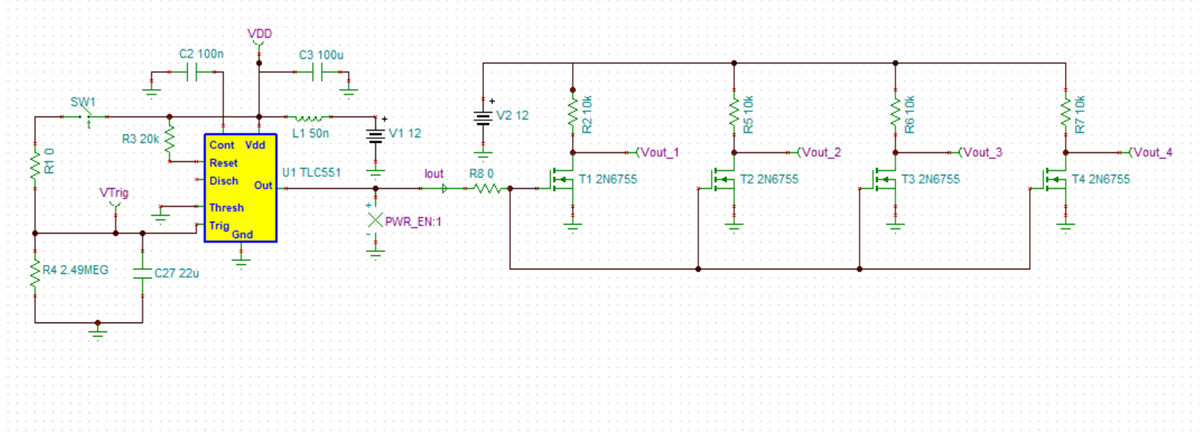

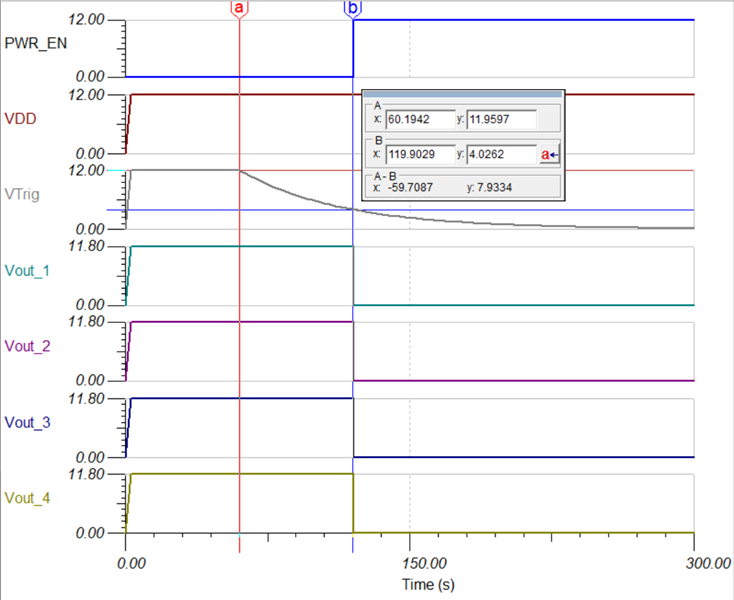

A time delay circuit with TLC551CD chip is used in the design with a 2.49Meg in parallel with a 22uF cap connected to the trigger input of the TLC551. The V+ is 12V, THRES connected to GND, CONT & DISCH pins floating. The input to a PMOS on the high side of the res/cap/trigger input that is initially in closed state (so the cap is at 12V), then the input opens the pmos and the res/cap start draining.

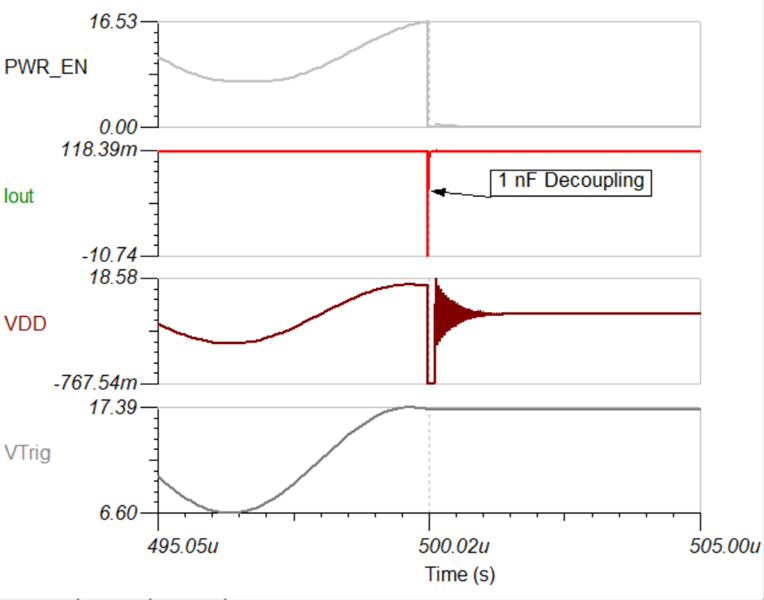

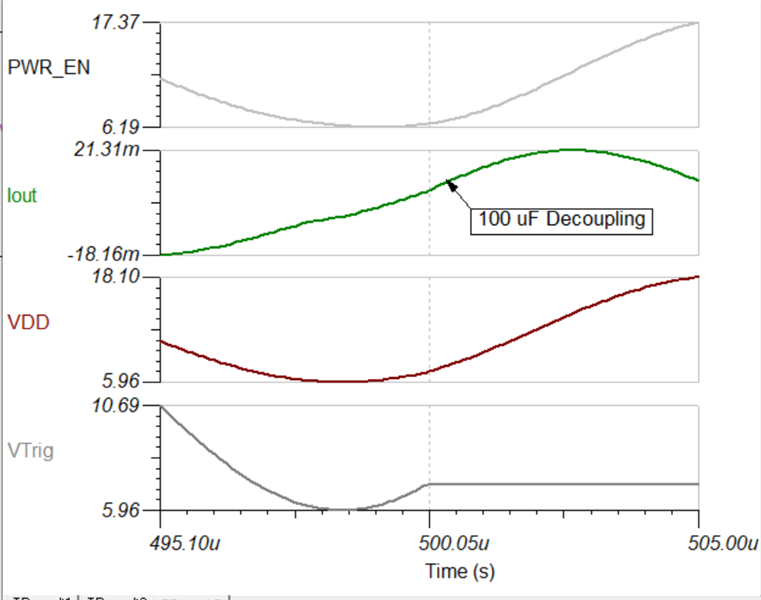

When the trigger input voltage reaches about 4V (where the 551 should trigger the output to change), the device is entering an oscillation where the trigger voltage will go back up to 4.3V, drain back to 4V and repeat endlessly. The 551 never changes state as a result. the 12V can be temporarily disabled, allowing the cap to fall down into the 2.5V range, and flip it back on and this will trigger the output to change state and stay there as it should.

Can you please help explain why the trigger input voltage is oscillating with this RC circuit. Is there some sort of capacitive coupling that is needed to resolve when the output flips? In monitoring the other pins during the issue, there is no oscillation on V+, Cont, or OUT. Only the trigger voltage is affected. The customer verified that none of the other inputs are changing.

Let me know if you need more information.

Regards,

Marvin