Hi,

we are using cdce62002, for converting ref clock of 13MHz to a clock of 204.8MHz.

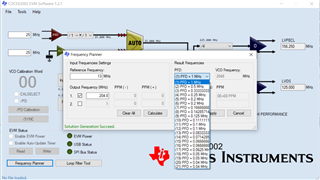

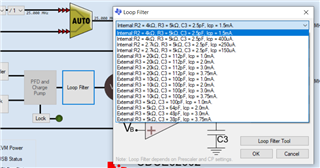

below is the configuration we are using.

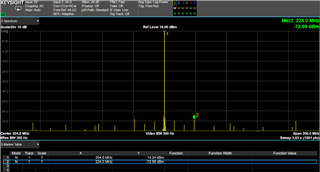

the issue is that we are facing many spurs at the output (please see attached screenshot of spectrum analyzer). these are quite low, but not low enough for our application...

my question: can you recomned of other confguration which can lower the levels of these spurs? or make them at higher offsets from carrier (i.e. move them away so we can filter out uisng bandpass filter)

thanks

Dan