Other Parts Discussed in Thread: LMK61E2, LMK61E0M, LMK6C

Hi,

I hope that you are doing well.

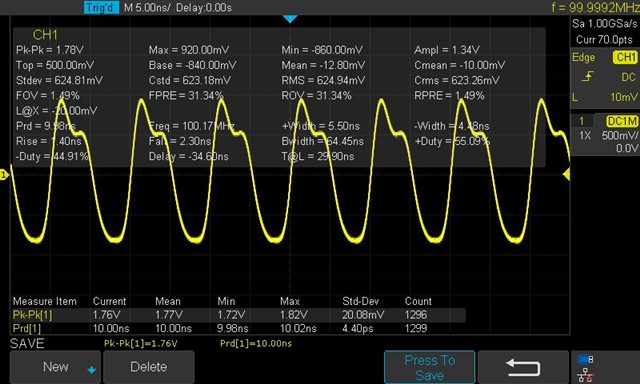

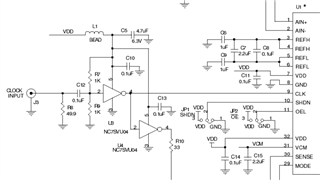

I have problem with module LMK61E2-100M00EVM.

I would like to understand what is the problem with the output clock?

Normally, it should be LVPECL format, but it is not and it is not in good shape too.

Thank you in advance for your reply.

Best regards.