Tool/software:

Hi ti team,

Could you please provide the configuration guide for LMX2485E? My client's new project is currently utilizing this component, but we are unaware of how to configure it. Thank you!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi There,

Please use TICS Pro to configure the device, you can also export the register settings to a text file.

Hi Noel,

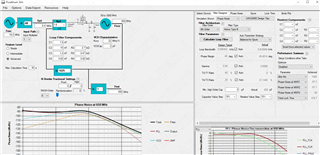

1. I successfully output the data needed to configure the registers using TICS Pro. Currently, the OSC is 19.2Mhz, and I only need to configure the RF high frequency to 650Mhz, the Fpd to be close to 200kHz (bandwidth), and the IF intermediate frequency is not needed. Therefore, the data is as follows:

R0 0xCB0000

R1 0xB0FA03

R2 0x001385

R3 0xFF00A7

R4 0x20C549

R5 0x00000B

R6 0x3C000D

R7 0x00090F

2) To make the LMX2485E work, I pulled LE low, CE high, and ENOSC high. During configuration, the CLK period was approximately 37us. After writing 24 bits of data to the register, I would pull LE high and 17us later pull it low.

Then there are the following questions:

1. I verified that the data and clock signals on the logic analyzer were normal. However, when I looked at the frequency with a spectrum analyzer, it was unchanged, and no matter how long I waited, the LD was not pulled up using a multimeter. Could you please provide a reference for the effective timing of Data and Clock?

2. Can you provide the driver for the EVM?

Hi switch,

According to your register setting, your configuration will be as follows, it does not match with your description.

you should change the configuration to below. Charge pump gain setting depends on your loop filter design.

Since you use IF PLL, you should set the MUX to IF lock detect output.

the final register value will look like below.

Hi Weldon,

Register settings look good. Schematic looks good.

You can use PLL Sim (www.ti.com/.../PLLATINUMSIM-SW) to design and simulate the loop filter.

The design is follow as(Vbias is 1.65V):

However, once I power up the PLL and VCO, the CpoutRF will soon drop to 0V, so as the output of the loop filter. The output of the loop filter also rise to 13V after it stay 0V for few seconds.

My start up sequence is CLK, Data, CE, ENOSC set HI, LE set LOW, after around 5ms, I start to write register values. I set LE HI for 18us then set it LOW for each address.

Hi Weldon,

To debug, let's see if you can make the following happen first.

1. Vcc power up

2. set CE pin = HIGH

3. Program LD pin to output a logic HIGH.

If you cannot measure HIGH at LD pin, you have programming issue. Capture the SPI waveforms to debug.