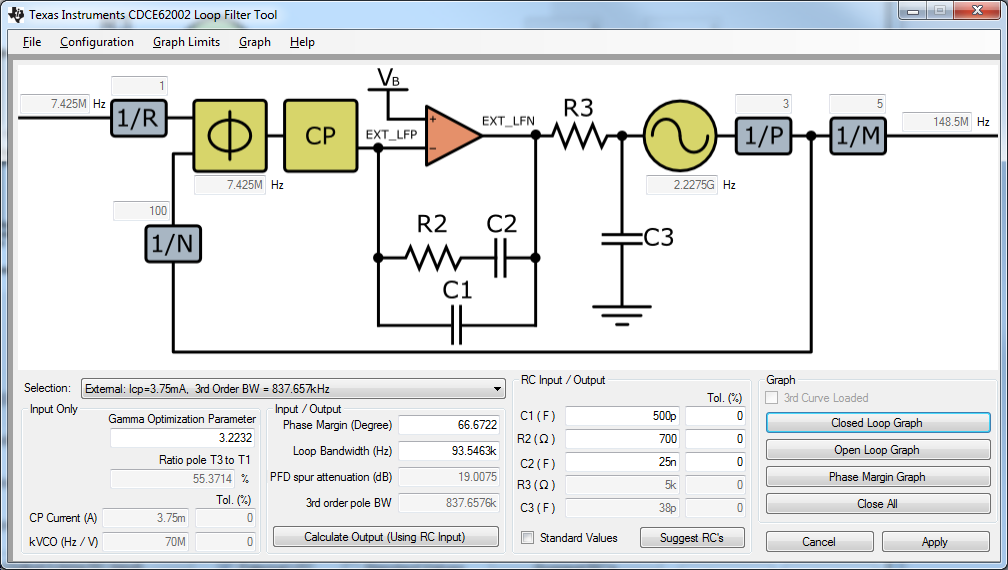

I am using the CDCE62002 to lock a HD video clock, output 74MHz, input 30MHz (approx).

From ambient, the CDCE comes up, and stabilises to acceptable jitter within 30 seconds. After about 4 minutes, the jitter increases, and then the clock output becomes unstable enough not to lock a receiver. After about another 2 minutes, the clocks stabilise and the jitter comes back to acceptable levels. After that, the clock output stays good all the time. Adding heat (by an air heat gun) during the unstable period almost immediately gets the clock correct. Adding heat from the start shortens considerably the early good period, and the bad period in the middle only happens for a couple of seconds. This seems to indicate that at a particular temperature the chip becomes unstable. Powering the chip down and up again when the chip is hot does not produce any problems. Any comments of suggestions .. maybe this is a known issue..