Other Parts Discussed in Thread: LMK1D1204

Tool/software:

Hello,

I am working on a clock distribution tree for an instrumentation chassis. Let me first describe the main blocks,

1) Precision LVDS clock oscillator with a clean output enable (allowing glitch free switching on and off). The frequency will be around 30 MHz.

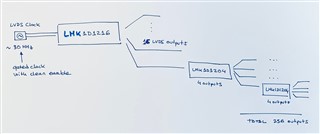

2) LMK1D1216 for making 16 copies of the input clock.

3) Two cascaded levels of LMK1D1204 devices.

In short, the tree makes 256 copies of the main input clock. Please, see the sketch attached.

Now the questions. We require that, when switching the main clock oscillator from OFF state to ON state, the first edge of the enabled clock arrives to all 256 outputs with a small skew. We can afford a maximum skew of 1000 ps, as we will calibrate the skew between the outputs afterwards,

- Can you confirm that LMK1D12xx devices are memory less? We have already discarded other clock buffers which include some sort of digital filter to detect if an incoming clock is present or not, introducing a variable 1, 2 or 3 cycles delay in the outputs after the input clock is enabled. With these other parts, some clock cycles are filtered out at the start. But out receivers (the instruments at the end of the distribution tree) need to receive and count all the incoming clocks pulses, each one of the 256 instruments has a time counter which must be synchronized globally.

- For estimating the skew between the 256 outputs, is it OK if I sum in quadrature the skew introduced by the LMK1D1216 (between different outputs) and the two layers of LMK1D1204s (which contribute both with adjacent part-to-part skew and same-part-outputs skews)?

Thanks for your help!

Jose Jimenez