Tool/software:

Hi ALL,

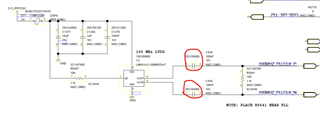

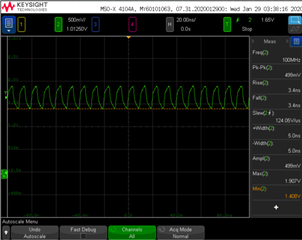

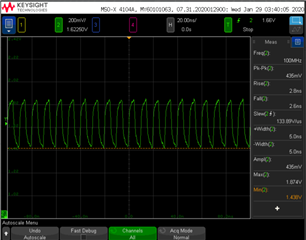

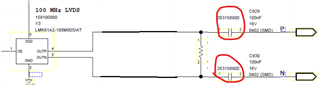

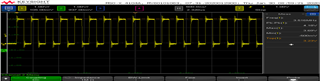

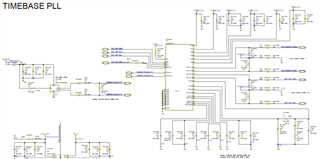

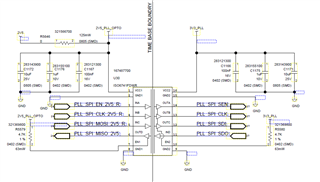

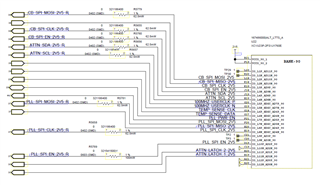

We’re using the LMX2582RHAT in our design, and we’re seeing some overshoot and undershoot on the SPI signals (CLK, CS, SDI). These signals are driven by an FPGA.

Here are the current drive strength settings:

PLL_SPI_EN: 12mAPLL_SPI_CLK: 12 mAPLL_SPI_MOSI: 12 mA

We’d like to know:

- is this overshoot & under shoot are within the acceptable limit?

- if not, can you please recommend how to reduce them

I’ve attached a signal capture of the SPI clock and the relevant schematic for reference.

Thanks

Sakthi