Other Parts Discussed in Thread: LMK3H2104

Tool/software:

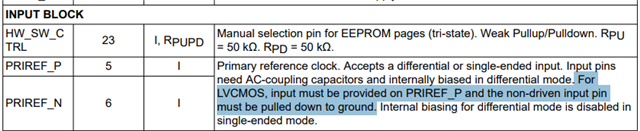

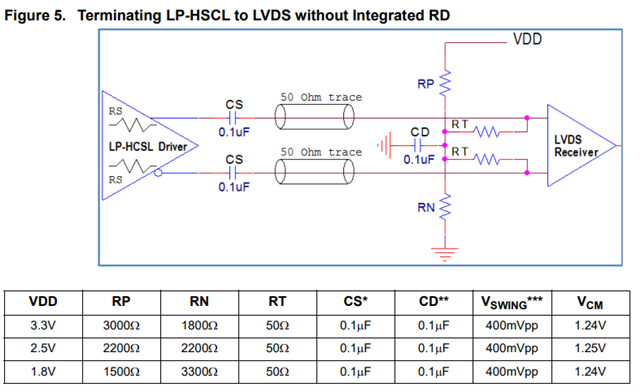

We are planning to use CDCLVC1310RHBR as the input source to CDCE6214RGET (configured for PCIe clock generation). Both devices are powered at 1.8V.

Can you please confirm:

- Is it safe to connect CDCLVC1310RHBR output directly to CDCE6214RGET input at 1.8V?

- Are there any known issues or recommendations for this configuration?

Thanks,

Pradeepraj M