SIR:

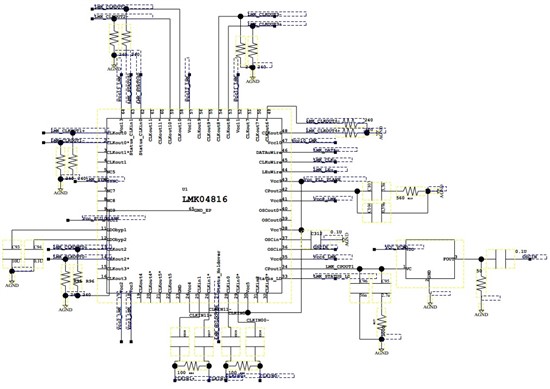

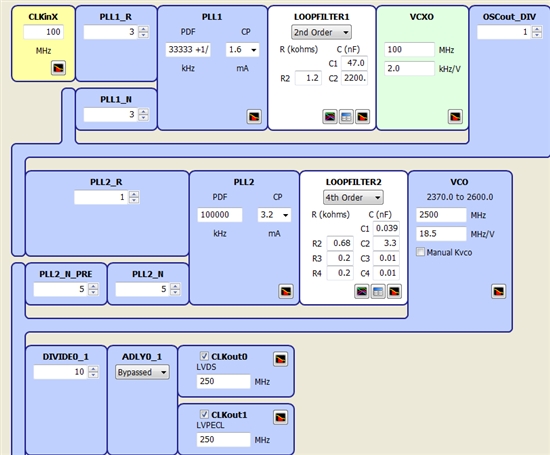

I use LMK04816 in my design for the first time in my design. I encounter some problems that is puzzled me.

I reset the device through the configure of register R0, then I configure register R0 to R31 according to my design. After that, clockout0, clockout2, clockout6, clockout8, clockout10 produce output clock in 250Mhz, which is coincident with my design. But:

-

I configure LD_MUX R[31:27]= 3, which means Status_LD pin is connected to “PLL1 & PLL2 DLD”. I configure LD_TYPE R[26:24]=3, which means the Status_LD pin is Output(push-pull).

But the Status_LD pin is not active. What is the possible reason for this problem?

-

When I test the output clock using oscilloscope, I find the 5 output clocks are not in the same level standard. In fact, I configure all the 5 clocks in the same level standard(1600mV LVPECL). Like, the peek-to-peek value for one signal of the differential of clockout2 and clockout6 is about 500mV, while the peek-to-peek value for clockout8 and clock10 is about 900mV. But for clockout0, one signal of the differential clock has a peek-to-peek value of about 900mV, the other has a value of 160mV. What’s the possible reason for this problem?

Regards

Thanks

Jacky

2014-01-18