Hello all,

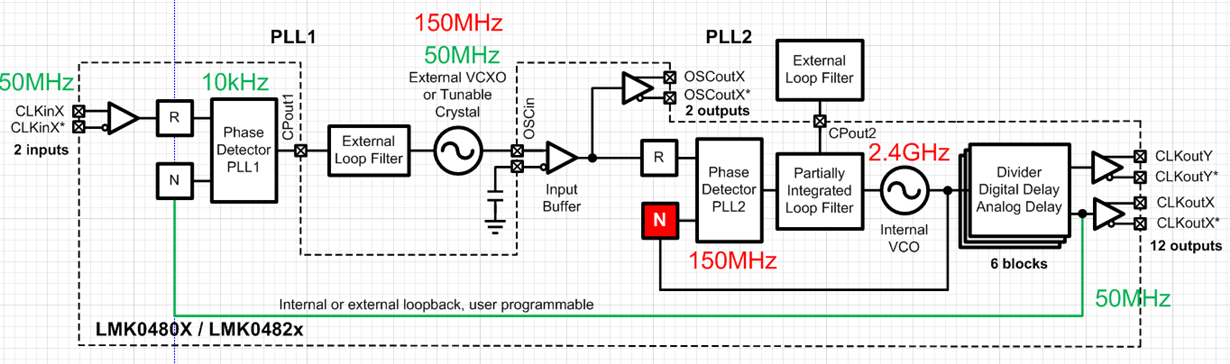

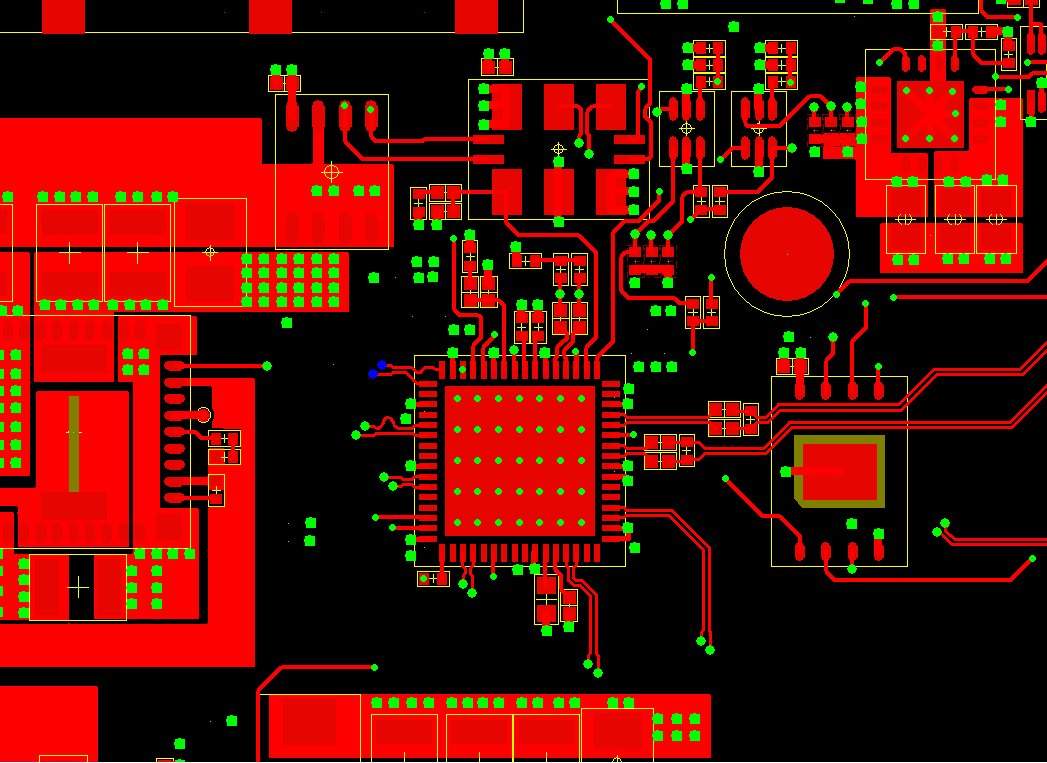

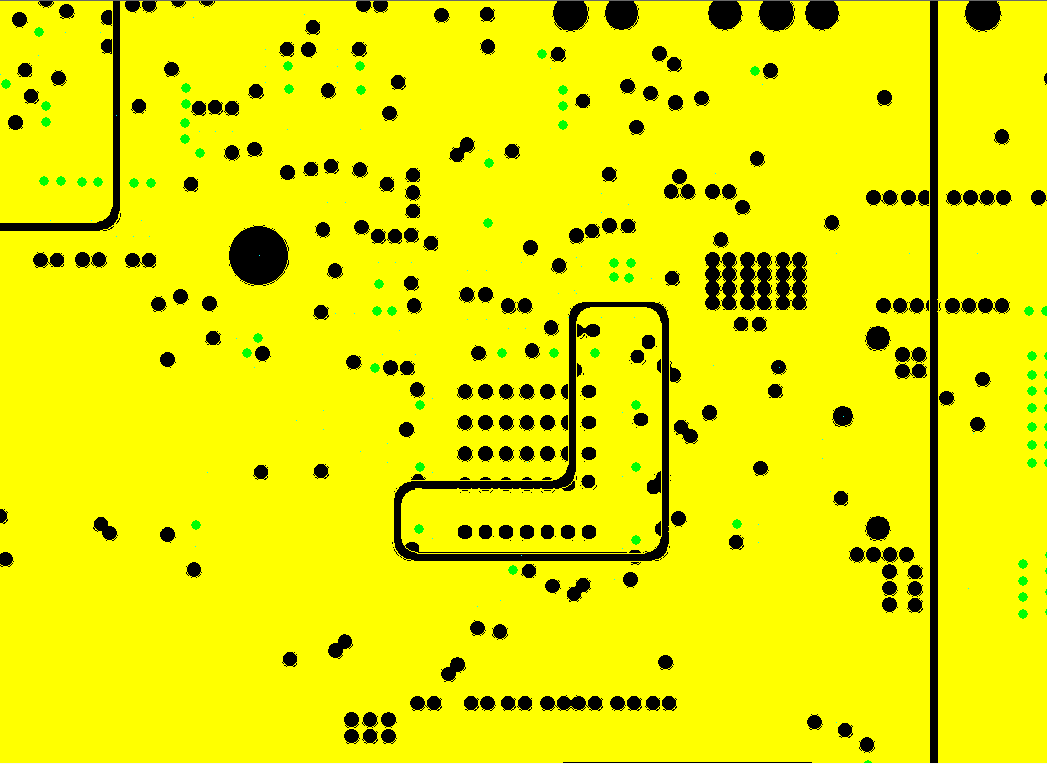

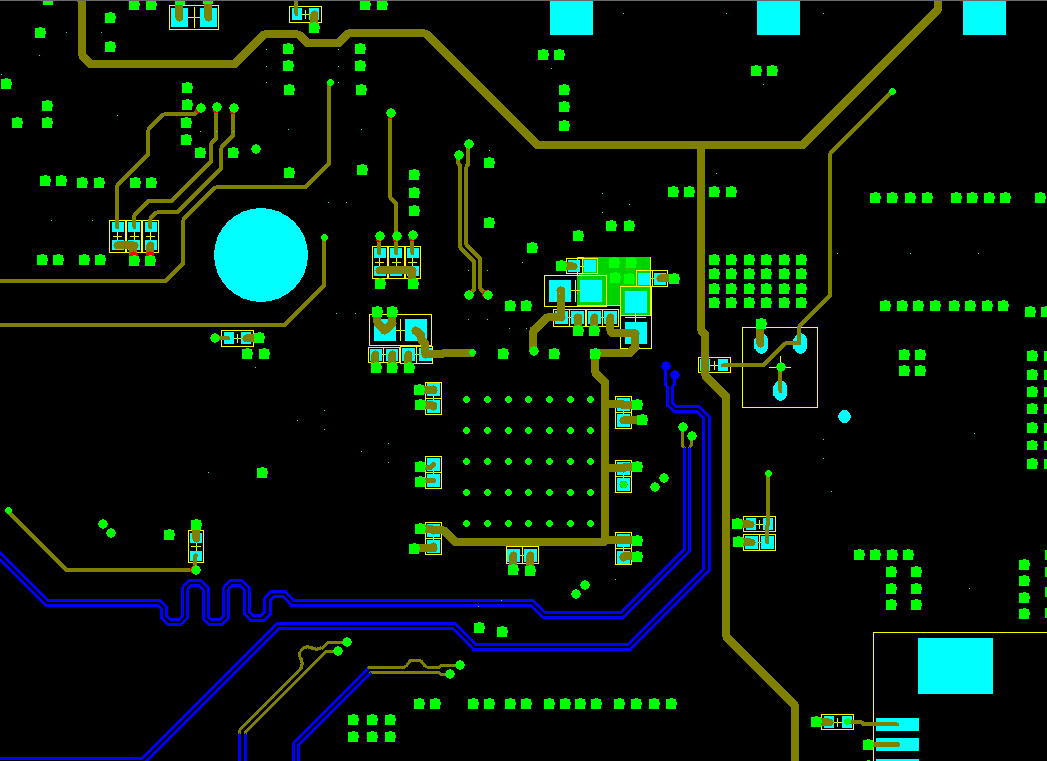

we are using the LMK04816 with the attached configuration (renamed to .txt, since .mac file upload is not allowed):

[SETUP] ADDRESS=888 CLOCK=4 DATA=2 LE=6 PART=LMK04816B PINPOSITION00=1 PINPOSITION01=7 PINPOSITION02=5 PINPOSITION03=10 [MODES] NAME00=R0 (INIT) VALUE00=2148925760 NAME01=R0 VALUE01=1312256 NAME02=R1 VALUE02=1312257 NAME03=R2 VALUE03=1312258 NAME04=R3 VALUE04=1312259 NAME05=R4 VALUE05=1312260 NAME06=R5 VALUE06=1312261 NAME07=R6 VALUE07=51773446 NAME08=R7 VALUE08=50528263 NAME09=R8 VALUE09=50528264 NAME10=R9 VALUE10=1431655753 NAME11=R10 VALUE11=2432846090 NAME12=R11 VALUE12=335556619 NAME13=R12 VALUE13=453771628 NAME14=R13 VALUE14=991105133 NAME15=R14 VALUE15=318767118 NAME16=R15 VALUE16=41975823 NAME17=R16 VALUE17=22348816 NAME18=R24 VALUE18=24 NAME19=R25 VALUE19=16842777 NAME20=R26 VALUE20=2947022874 NAME21=R27 VALUE21=470082075 NAME22=R28 VALUE22=2417180 NAME23=R29 VALUE23=41943325 NAME24=R30 VALUE24=33554718 NAME25=R31 VALUE25=2031647 OSCIN00=50 EXTRA_PLL_N_DIV_1_00=1 OSCIN01=150 EXTRA_PLL_N_DIV_1_01=1 PINS=513 [BURST] COUNT=0 [FLEXHASH] HASHVALUE=0

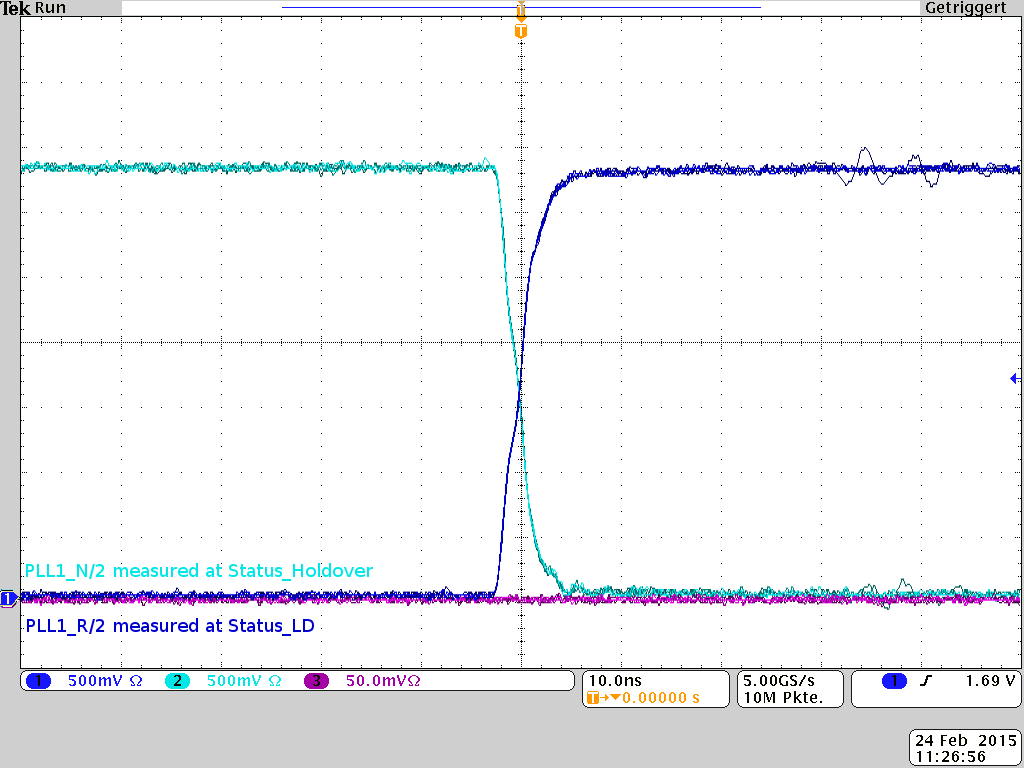

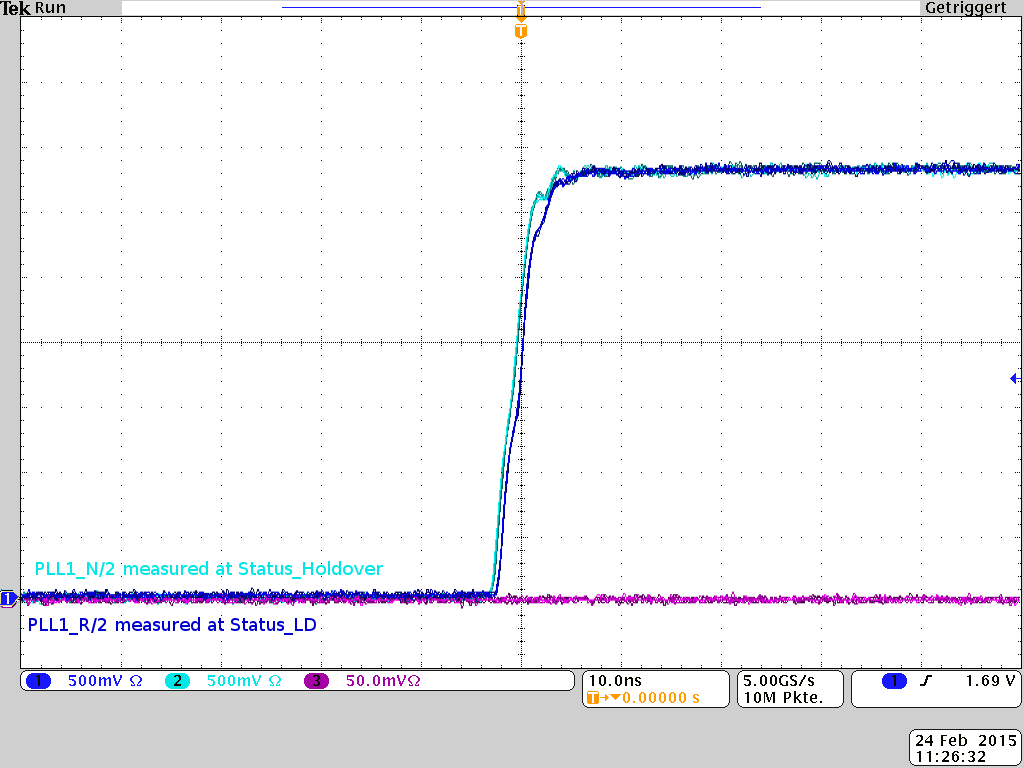

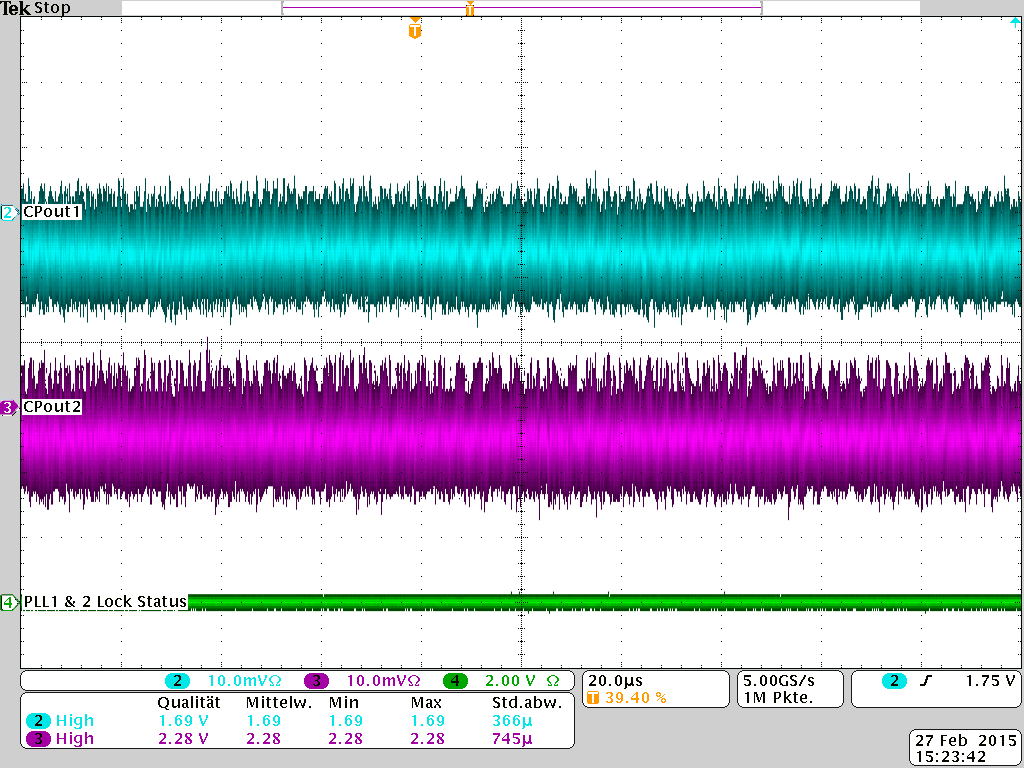

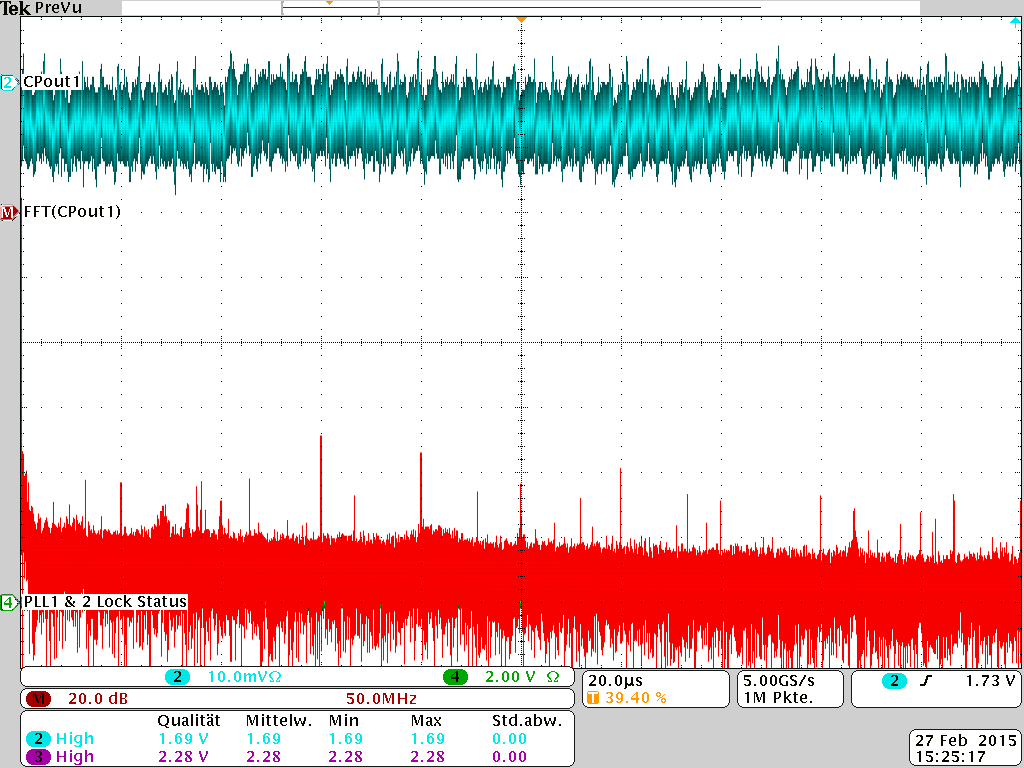

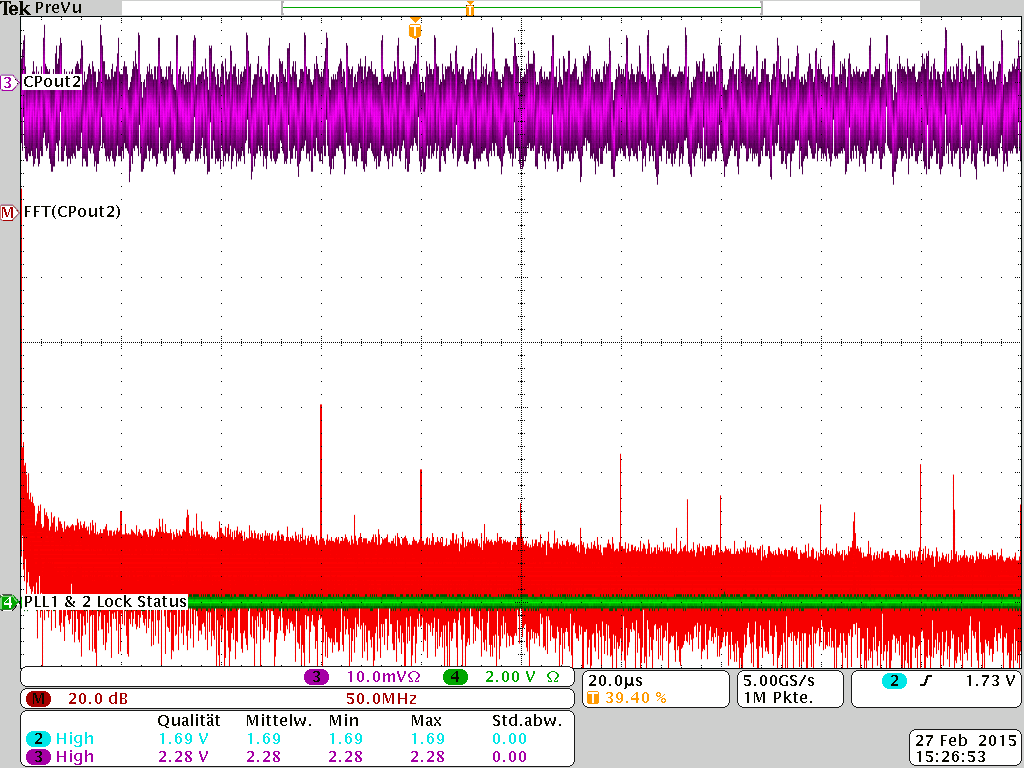

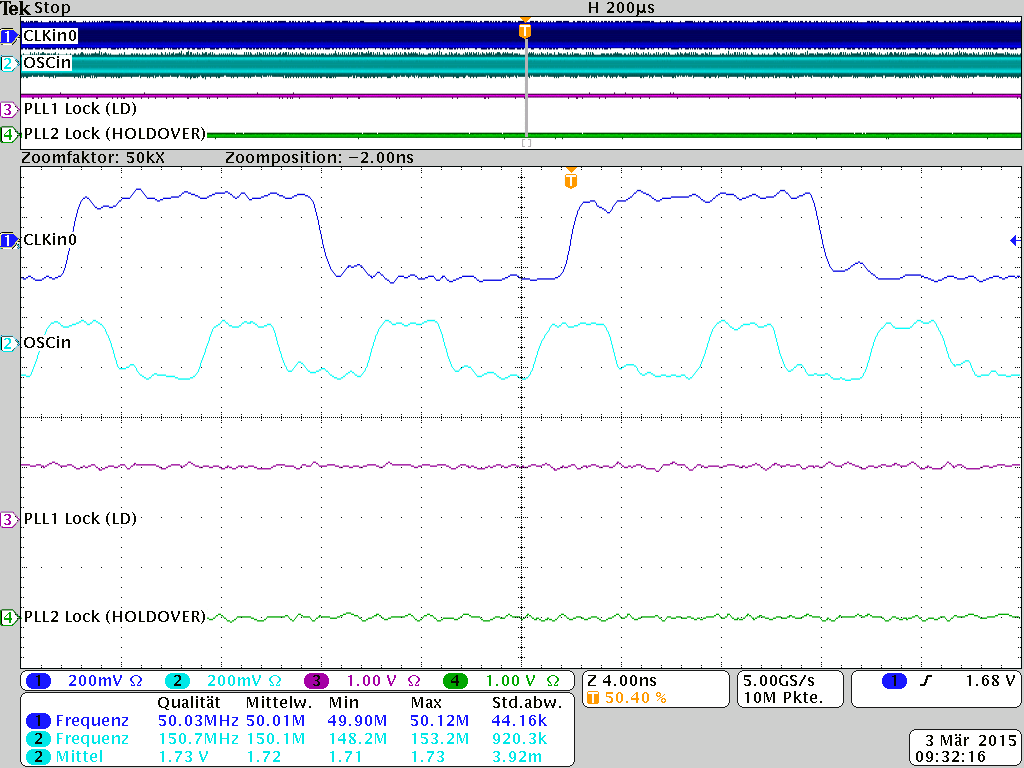

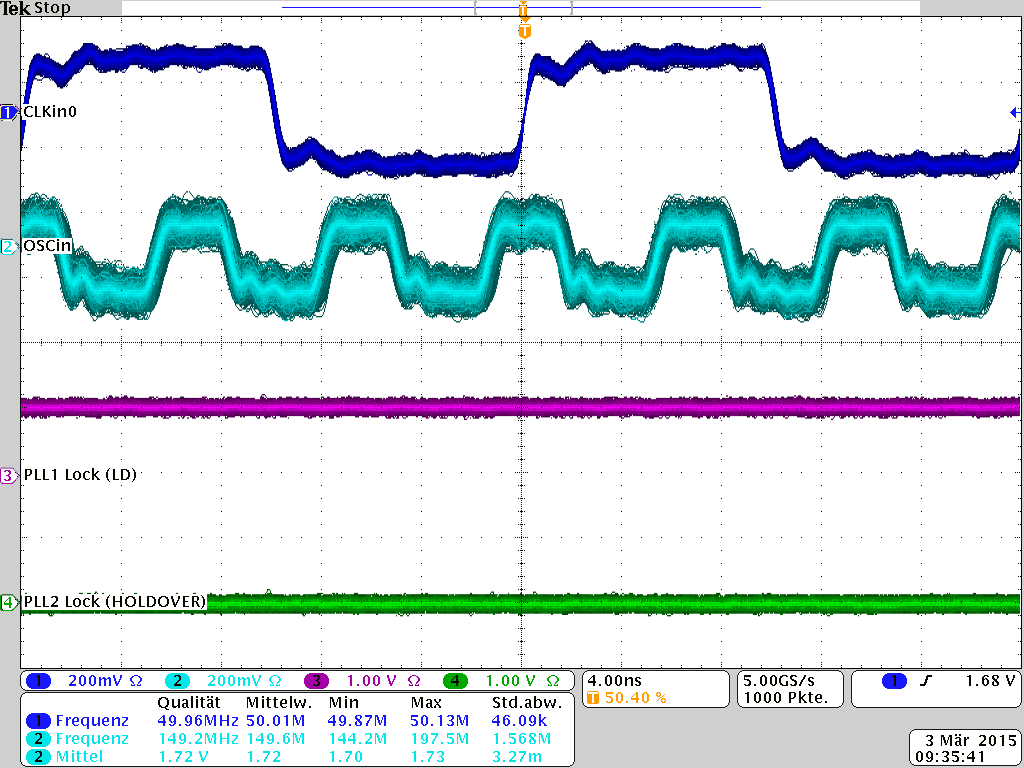

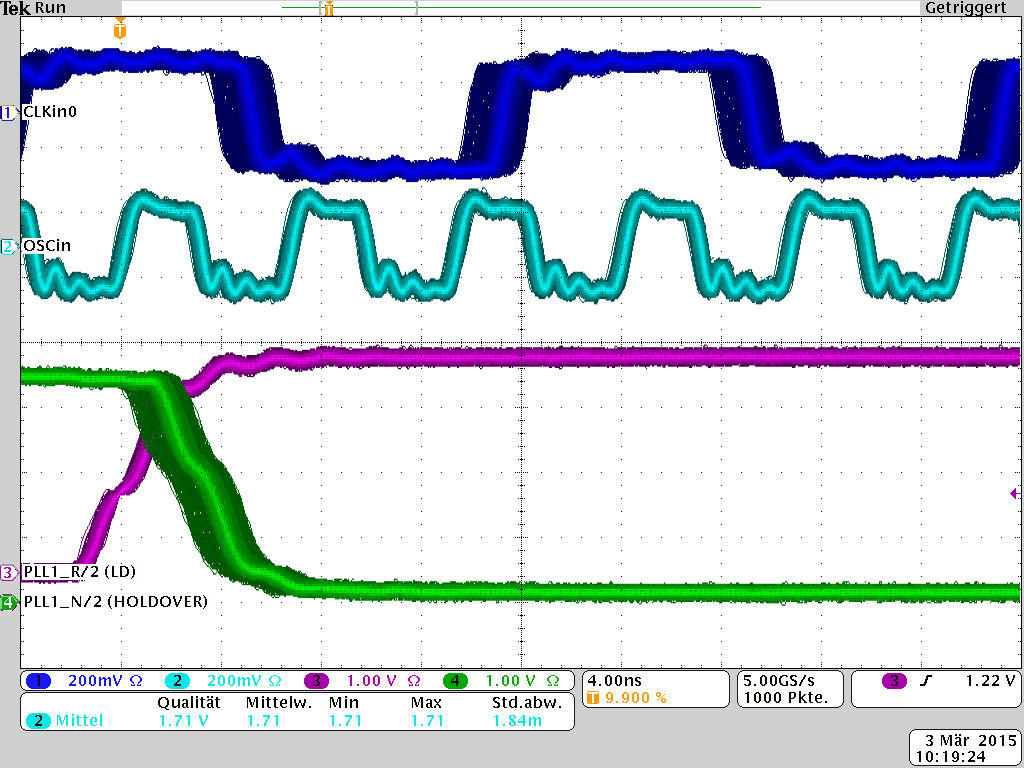

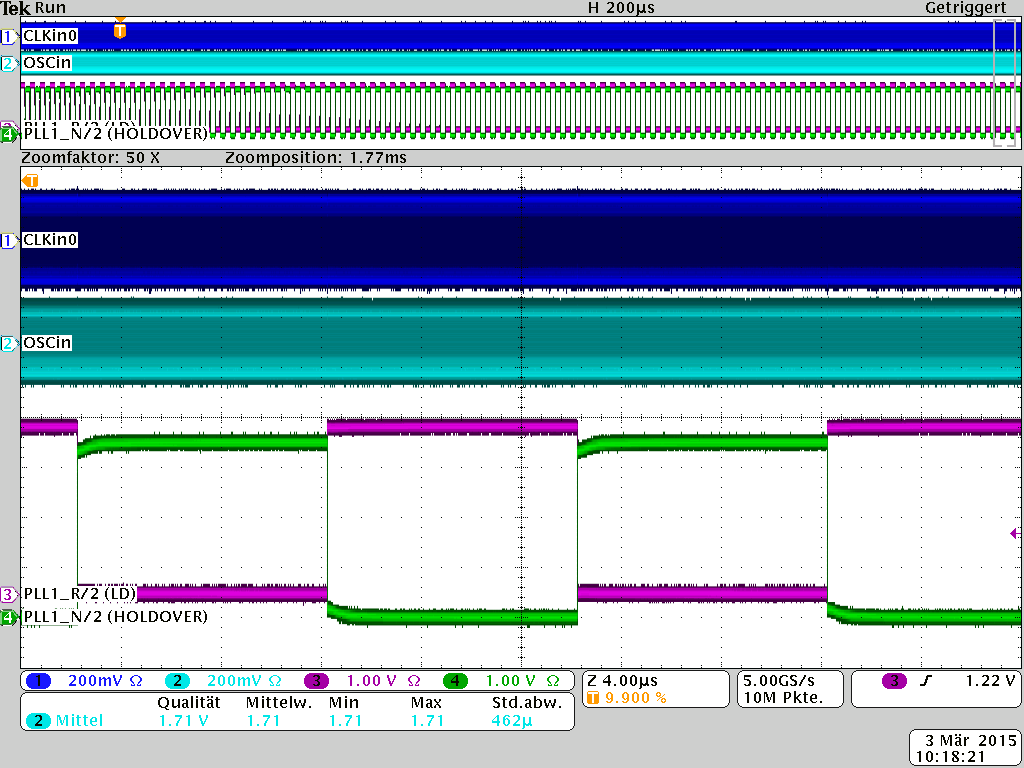

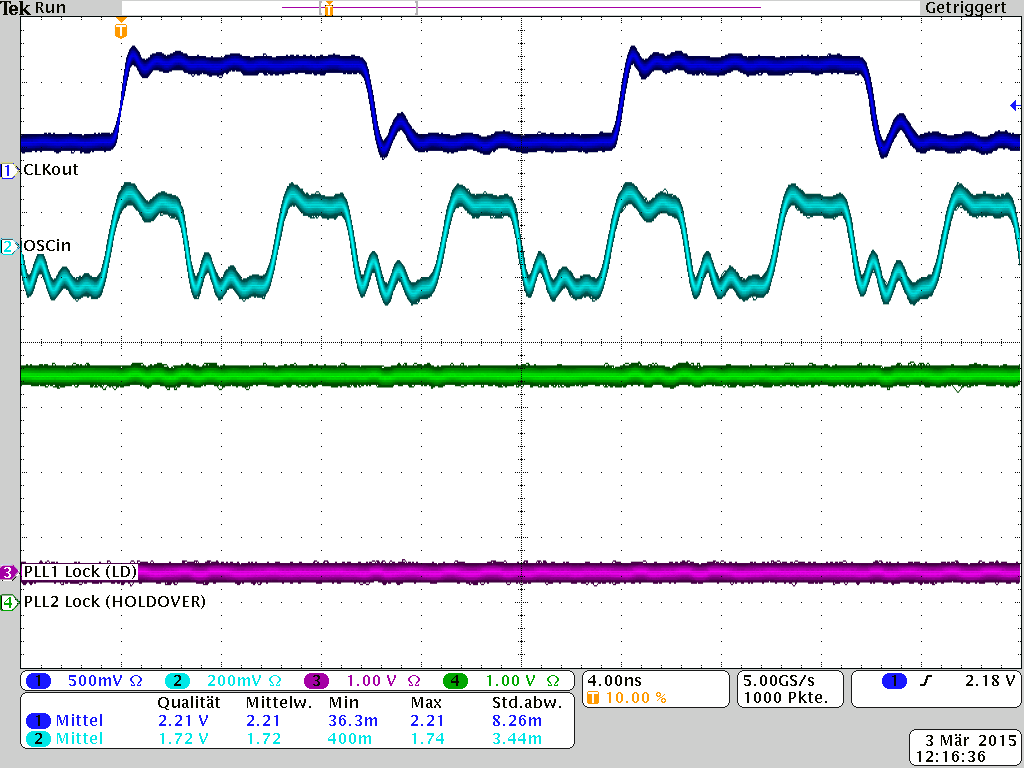

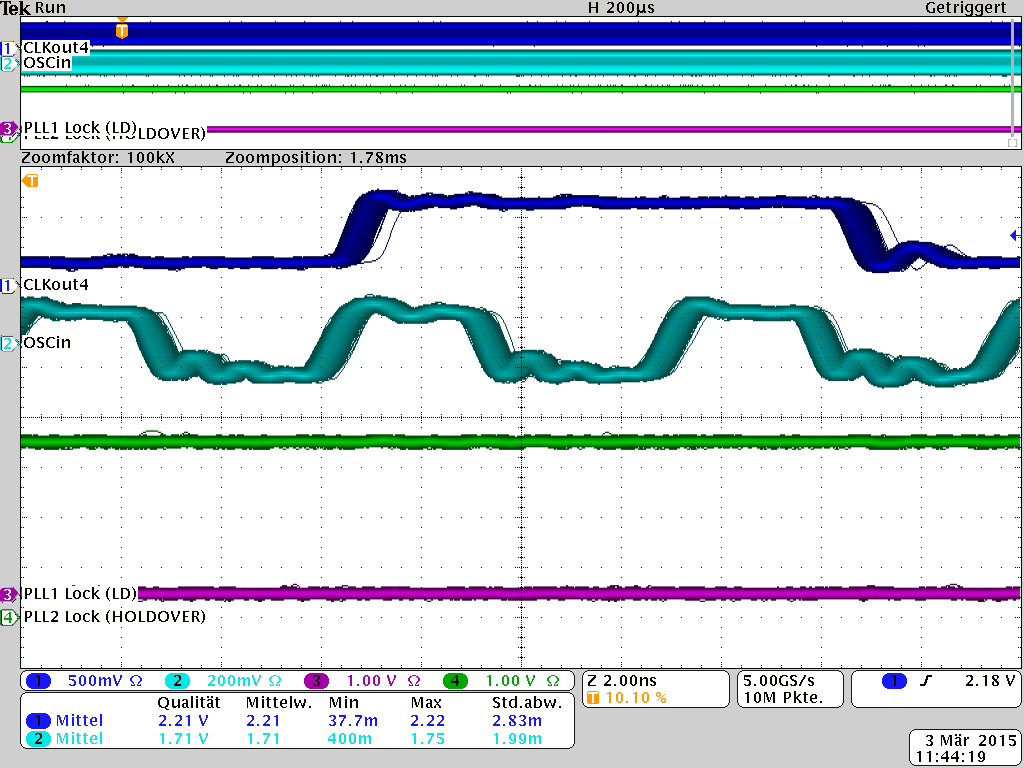

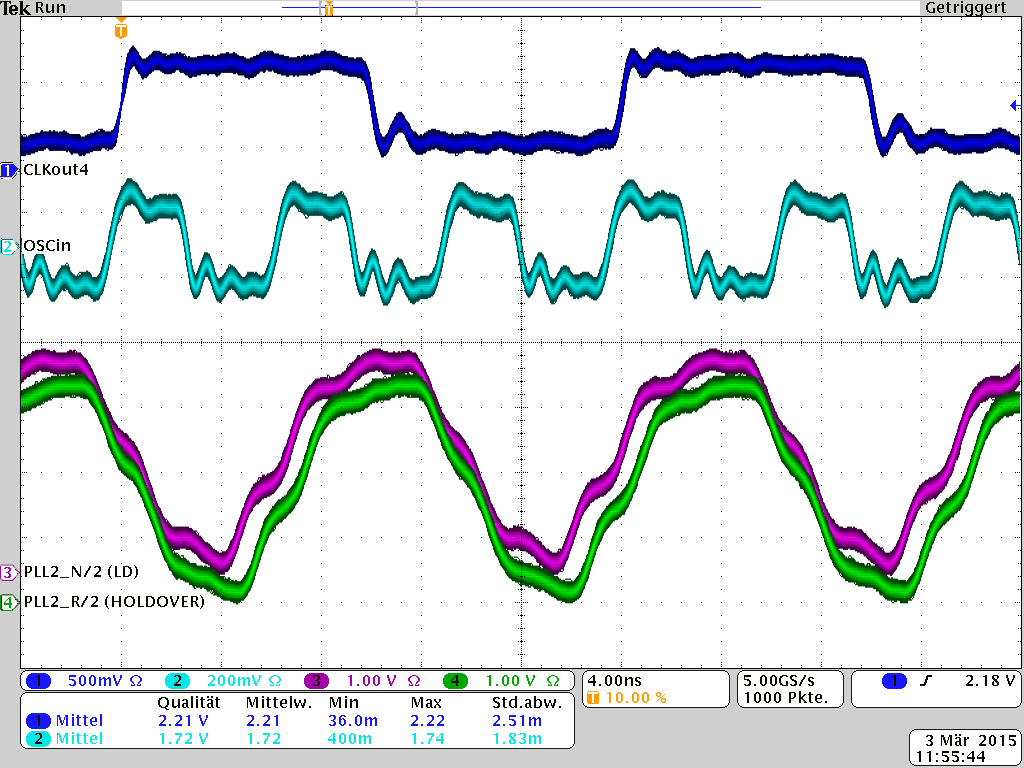

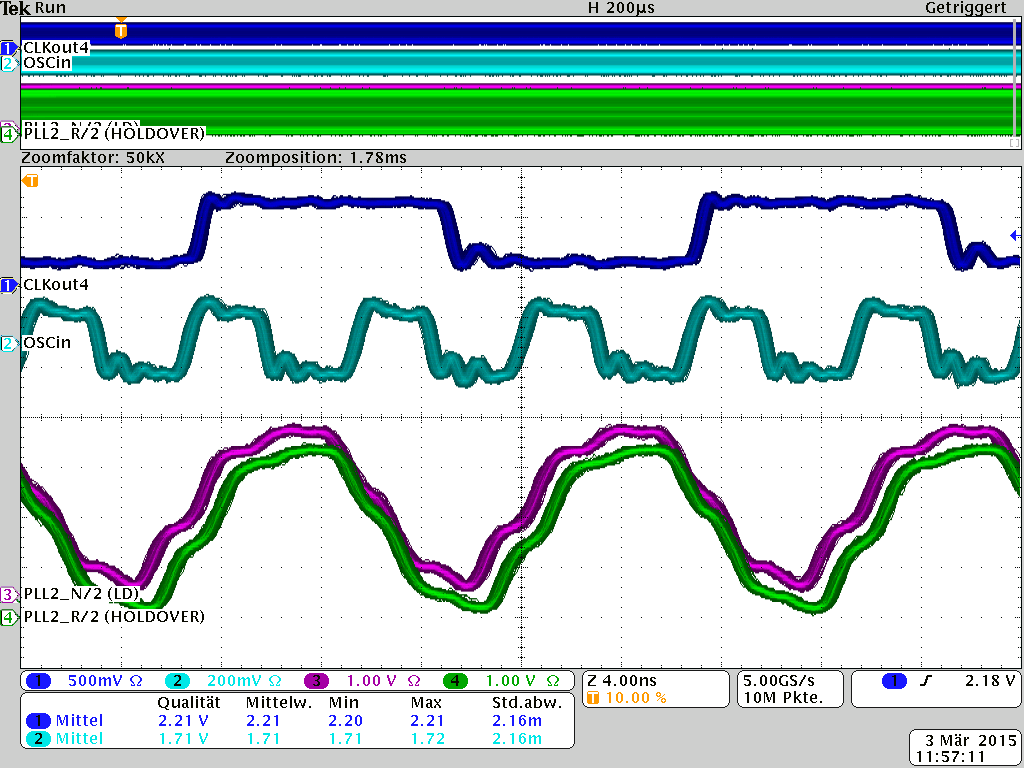

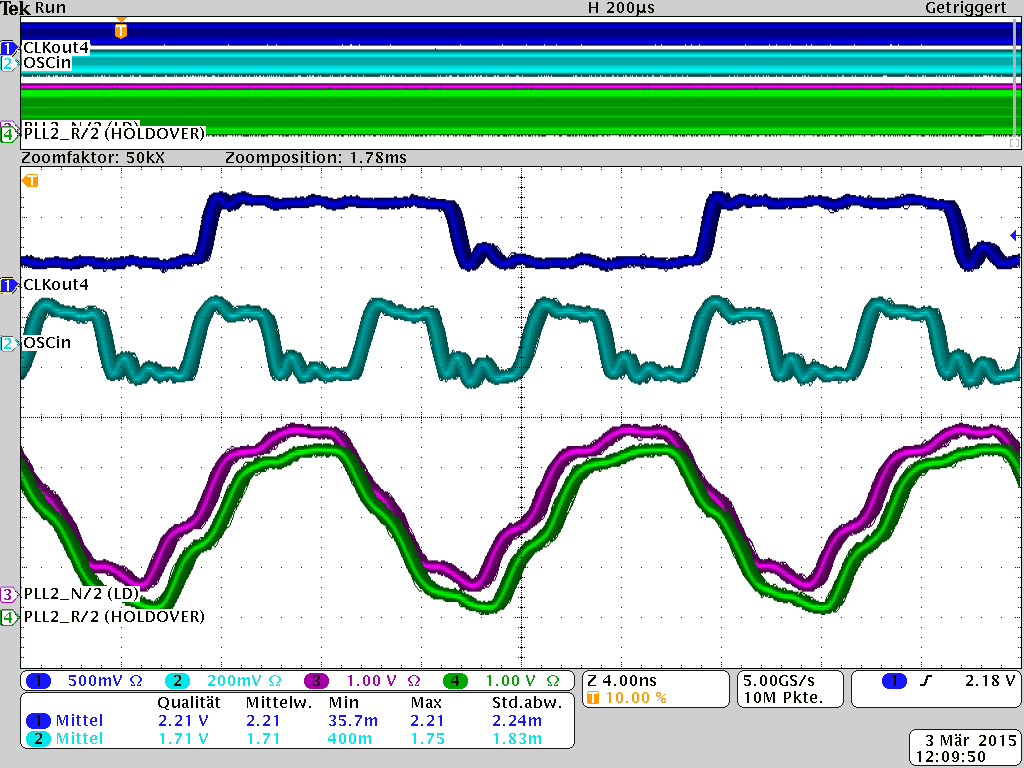

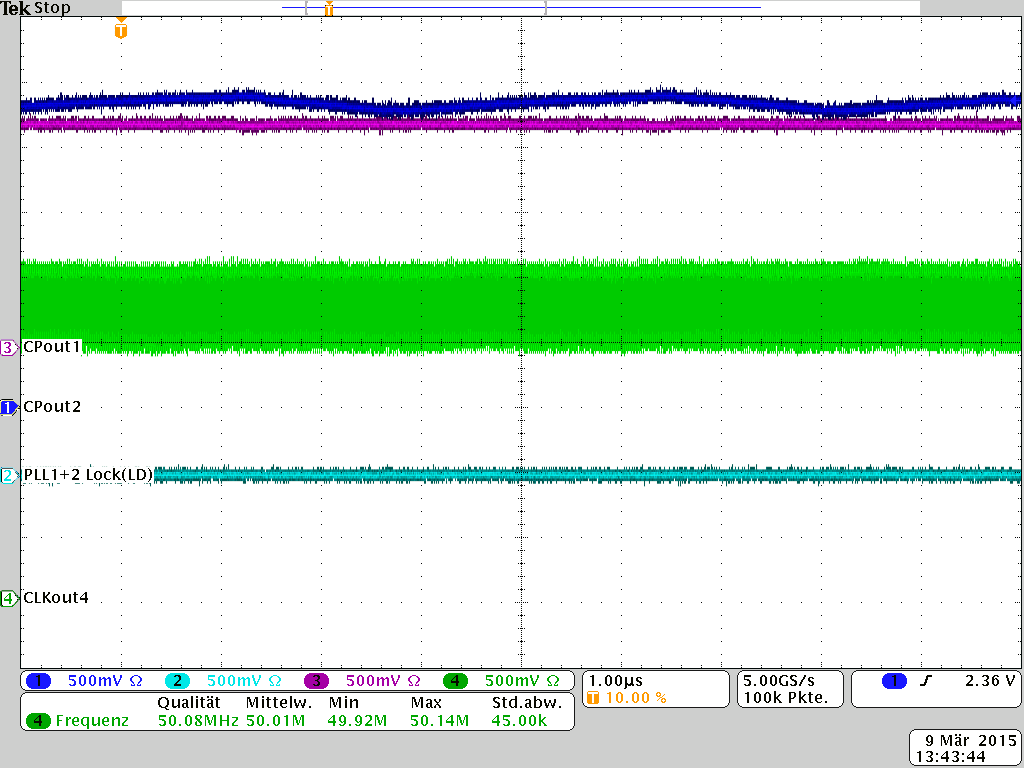

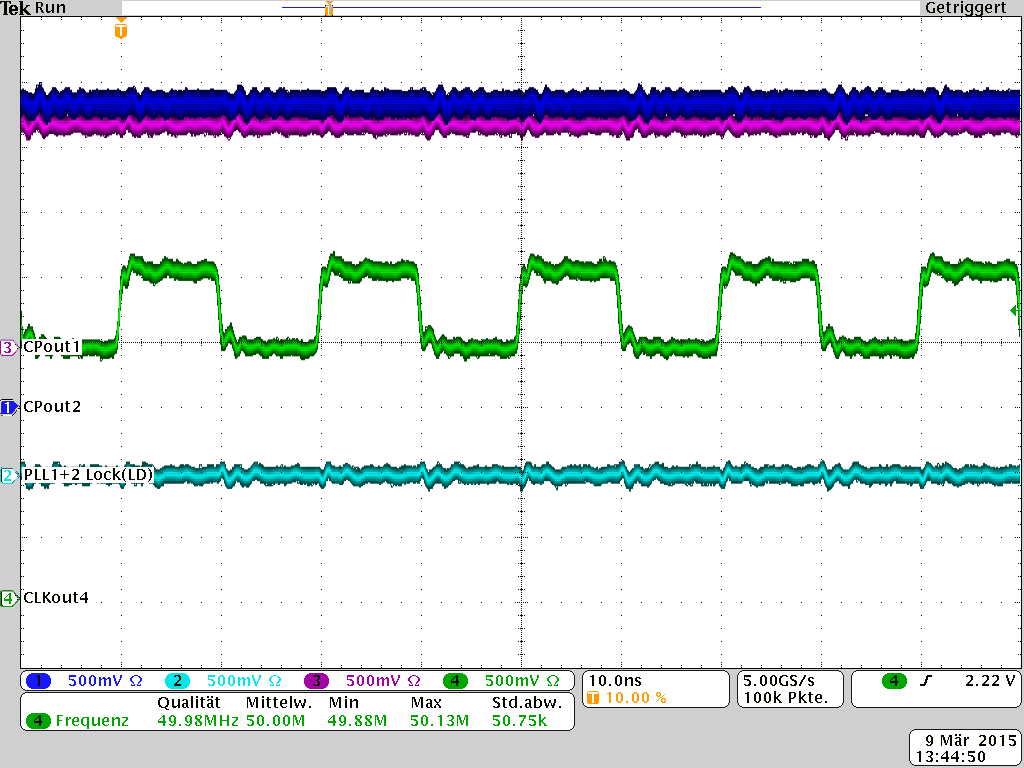

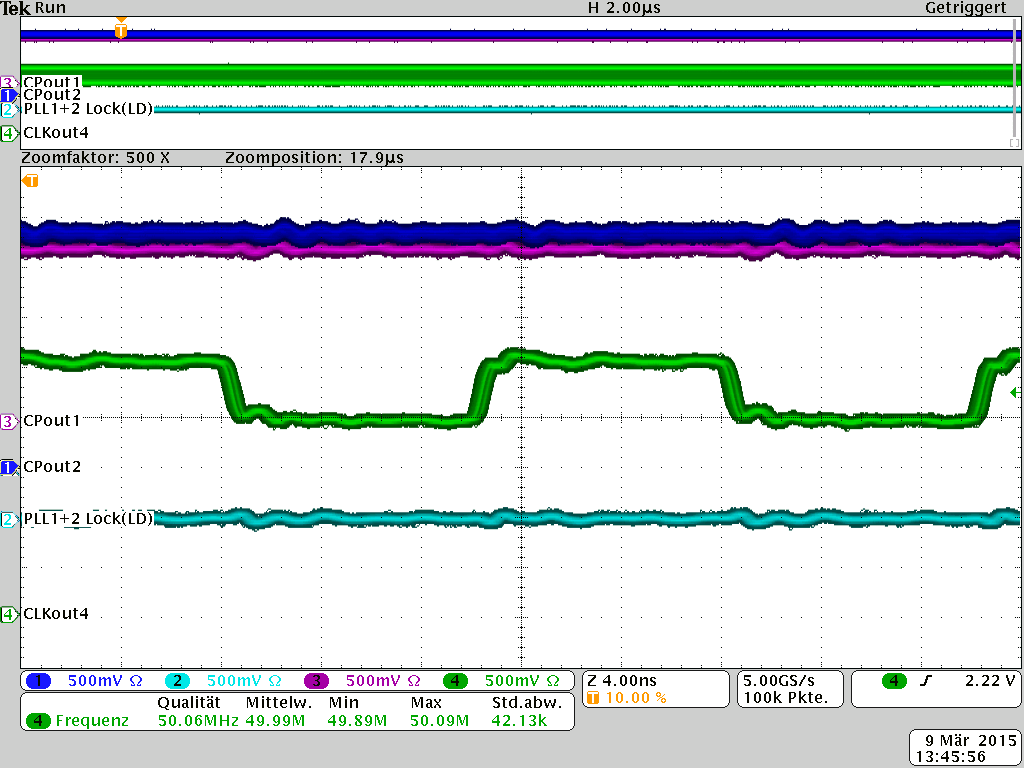

Output frequencies are as desired, but we fail to see a PLL lock on the LD_Status pin (LD = 1).

Can you please have a look into the register set and give me a hint?

Thanks in advance,

Niels