Other Parts Discussed in Thread: CDCLVP2102, CDCLVP1204, CDCVF2505

Hi team,

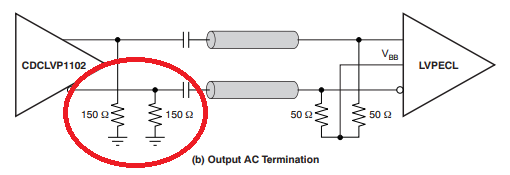

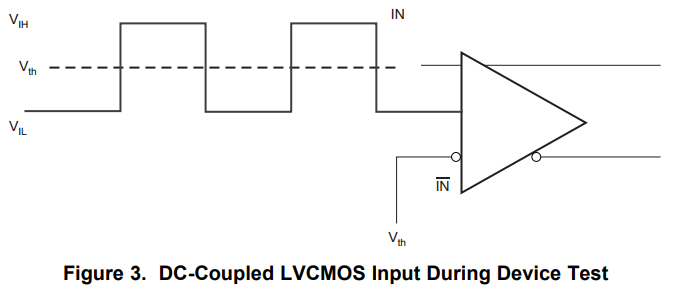

The customer is using CDCLVP1102. He uses the single-ended input. He tests the Vac_ref pin and it has a 2V voltage.

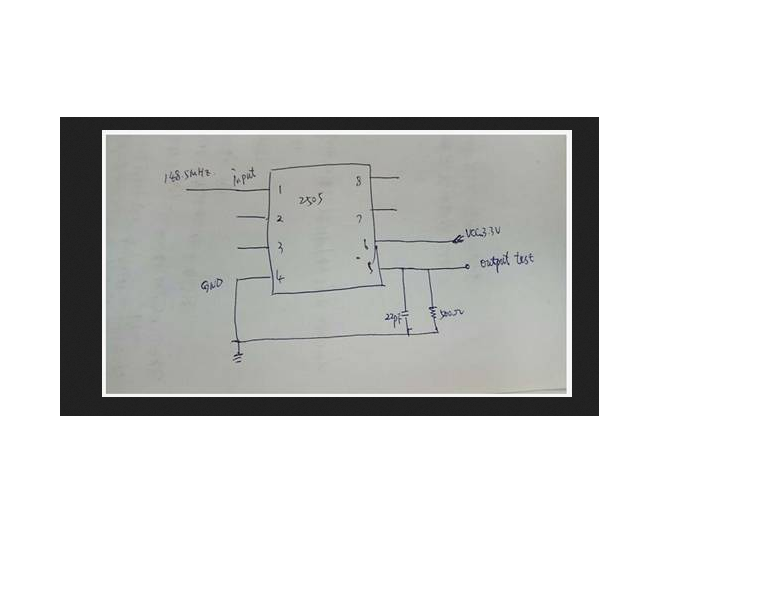

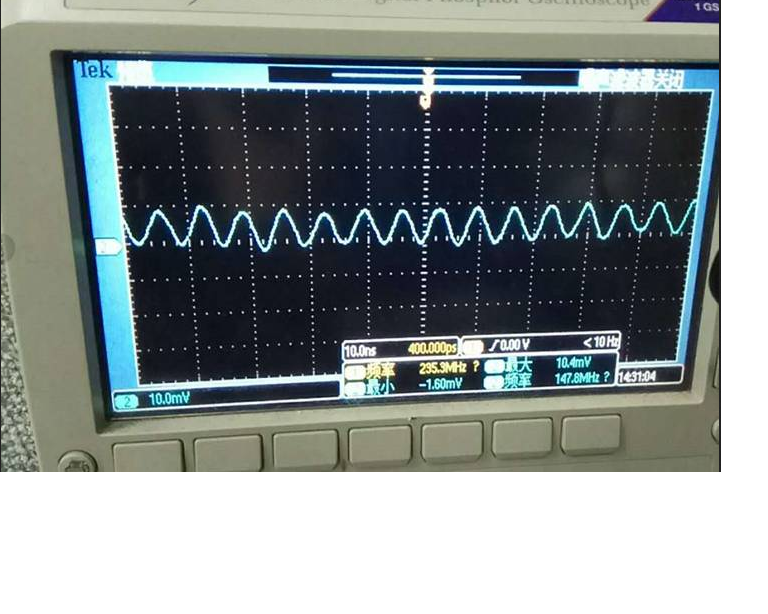

The schematic is in the attachment. When he uses 148.5MHZ or 200MHZ as the input clock frequency,but there is no output signal waveform in

the oscilloscope.He uses LVPECL to output.

Would you provide some suggestions for the customer's issue? Is his schematic correct?

Best Wishes,

Mickey Zhang

Asia Customer Support Center

Texas Instruments