Hello,

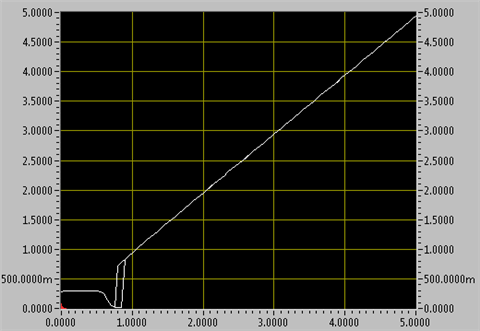

On the TLC551, the output is showing low while the Trig pin is low, and the Thresh pin is high, but the Trig is supposed to override Thresh. This problem usually occurs while operating the device at Vdd below 1.3V, although sometimes at higher voltages. All measurements are taken upon initial power-up of Vdd with a slew rate of about 1V/us; sometimes faster. Reset is tied to Vdd, and the behavior persists with or without manipulation of the Control pin.

At 1.3V Vdd, with the Trig pin and Thresh pin capacitively coupled to GND and Vdd respectively(12nF both), the output undesirably goes low. If only the GND coupling cap is replaced with a dead short to ground, the output successfully stays high. However, even with the dead short in place, when Vdd is lowered to 1.1V, the output again undesirably goes low. EMI effects have been observed, but the phenomenon persists even when partially addressed. It is important for this application that the output initially be high, and stay that way at least until Trig is pulled above it's trigger voltage. The pin priority of Trig overriding Thresh is an important property to preserve. If Trig and Pin are tied together, and then coupled to GND , the output successfully goes high. However, tying them together is not the desired arrangement.

Any thoughts, solutions? It is desirable to avoid placing any parts in the path of the main branch of the positive supply rail.

Thanks