- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

Our customer would like to double check the period of START pulse.

In case of single-cycle settling configuration, the period of start pulse is more than tSETTLE. It doesn’t include the period of 24 bit data output from DOUT (1.2us@fclk = 20MHz).

Is that correct ?

They think the conversion data would keep if DRDY is asserted. But even in single-cycle settling, Data will be flushed if START is asserted again before asserting DRDY.

Thank you and best regards,

Michiaki

Hello Michiaki,

Yes, that is correct. At the end of t-settle time period, DRDY will transition from low to high, and then the data must be clocked out of the device. This will result in an output data rate period that is longer than t-settle.

After data retrieval, you can then pulse the start pin again to start the next conversion.

Regards,

Keith Nicholas

Precision ADC Applications

Hi Keith,

Please let me double check.

What you means is that the conversion data should be kept when DRDY is asserted because it is converting data that it is flushed.

While conversion data will be flushed if START is asserted before asserting DRDY even in single-cycle configuration.

So , to keep conversion data, the period of START should be longer than tSETTLE and not including the output time of 24bit via DOUT.

Is my understanding correct ?

Thank you and best regards,

Michiaki

Hello Michiaki,

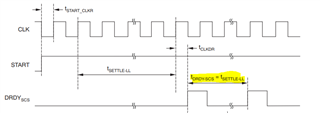

The output data period, or the total period of START, will be longer than tSETTLE. The START pulse width must be at least 1 tCLK period, then wait for DRDY to transition from low to high (tSETTLE), and then clock data result out of device. After this, you can issue another START pulse.

The other option for single cycle settling that will result in a slightly faster output data rate is to set the START pin high and keep it high, wait for the rising edge of DRDY (tSETTLE), clock the data out, and then wait for the next DRDY rising edge. In this case, the output data rate period will be tSETTLE, Figure 25.

Regards,

Keith Nicholas

Precision ADC Applications