Other Parts Discussed in Thread: ADS1282, ADCPRO, ADS1261, OPA1632, ADS1262, REF70

Hi,

We bought a ADS1282 EVM PDK kit. Kit is working fine.We are using adc pro software for configuring and analysing ADS1282 EVM PDK kit.

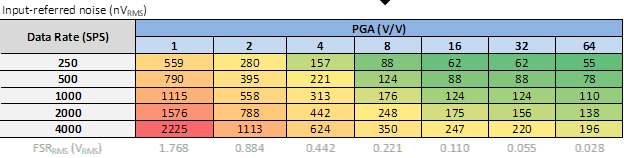

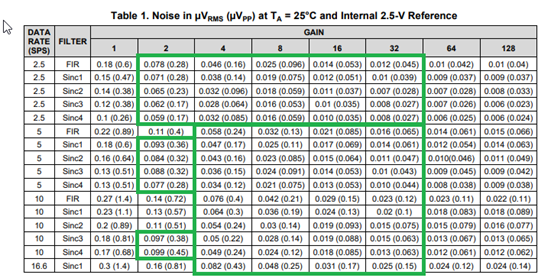

We are applying 10mV input to channel 1 of ADS1282 with following configuration sinc+lpf filter selection, 250sps,pga=1,chop ON the counts come around the

calculated value(Counts varying from 4337187 to 4351272). But when i use same configuration with sinc+lpf+hpf filter selection the count is wrong

(Counts varying from -6464 to 7745). We need a speedy solution to our problem .

Regards,

Venkatavel