Other Parts Discussed in Thread: DAC8718

Hi

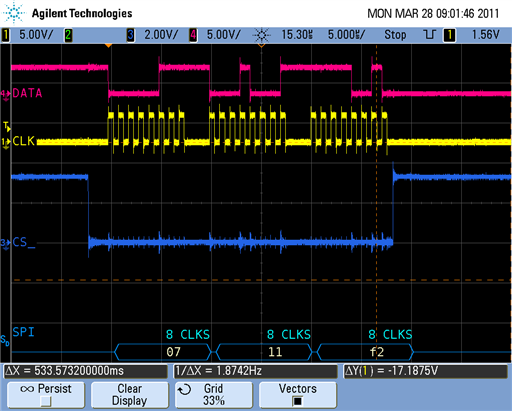

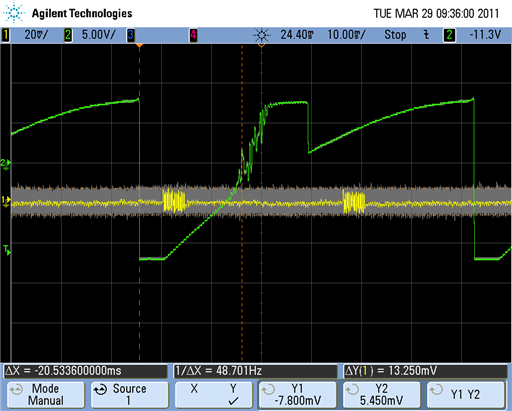

I have a problem with the DAC8718 converter: I can't get a correct output. The 2nd (green) channel in a picture below is a DAC output formed by sending a state of 16bit counter to the DAC broadcast register from 0000h to FFFFh. DAC is powered with +-12V source and reference if 4.096V.

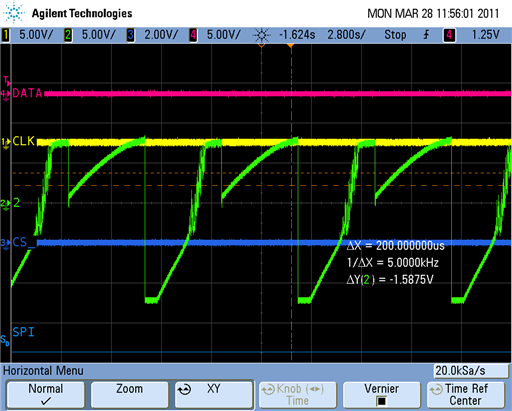

I expected to get a sawtooth style voltage from -12V to +12V with saturations. But the result I have got is far from the desired result. It starts from about -12V as expected but finishes at about +7.5V and the voltage shape is not linear.

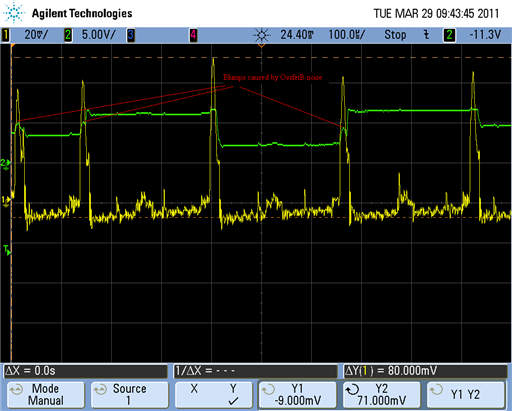

The next picture shows an excange with DAC. The result of sending 23C0h and 23C1h codes is about -9.7V output.

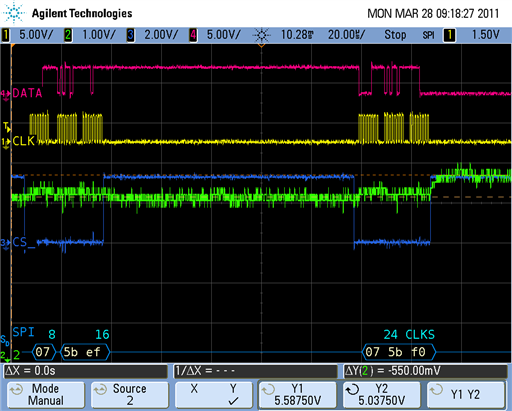

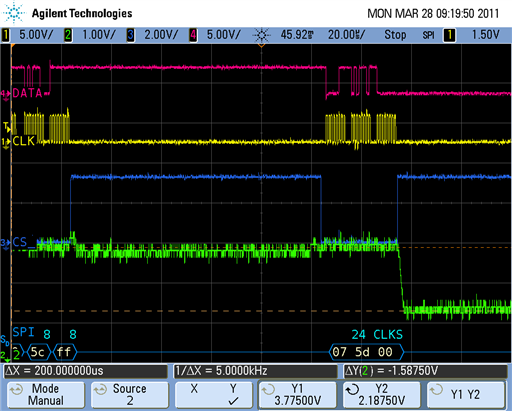

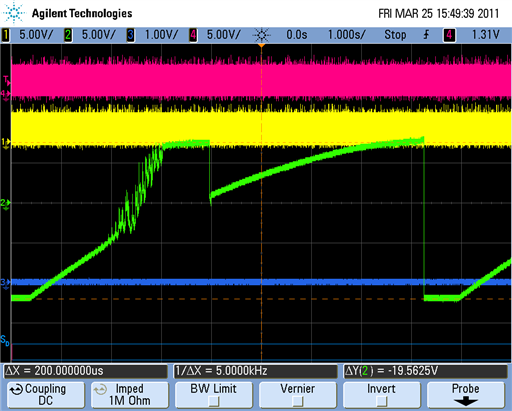

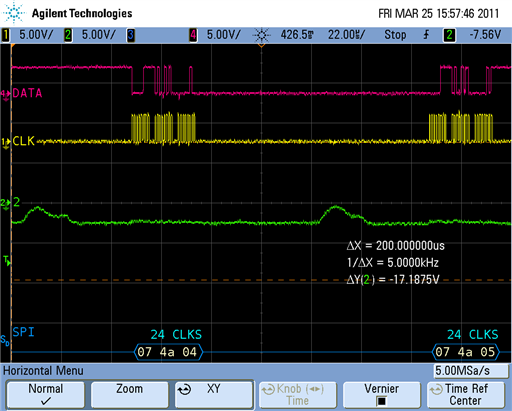

The next few pictures show the most strange sections of the voltage shape.

May be somebody knows how can I obtain a normal operation of this converter?

Thanks.