Other Parts Discussed in Thread: LMK04832,

Hi,

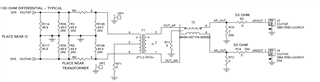

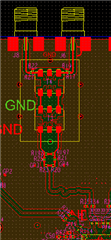

We have used 3 TI DACs of part number DAC39J82IAAV for Analog output generation. LMK04832NKDT is used for generation of JESD204B clocks and sampling clocks.

The schematic section has been attached, please provide review feedback for the design.

Design use details:

- All DACCLKP/N - AC coupled, LVPECL, 2520MHz

- All SYSREFP/N - Set as per lane rate and system clock frequencies, AC coupled option for DC coupling, LVPECL(AC coupled) LCPECL (DC coupled), <20MHz

- DAC WB,NB analog out (U31) - OUTAP/N: 407.5 ± 30 MHz, IOUTDP/N: 70MHz ± 2.5 MHz,

- DAC LO 1 analog out (U32) - OUTAP/N: 223.5 - 311.4 MHz

- DAC 3 analog out (U53) - OUTAP/N: 405 ± 37.5 MHz

- LMK Clock In 1 - 360MHz