Other Parts Discussed in Thread: ADS8881

I recently bought this ADC and I want to connect its output (conversion result) to the FPGA.

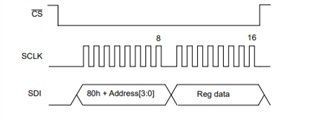

- How do I use it like a very simple ADC (analog in digital out), no registers, no programming etc. should i just feed the SDI pin invalid commands from the Master ?

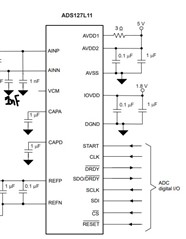

- Do I need to connect every pin to something ?

- If my analog input is single ended, do I just connect the negative analog input with GND?

- Can I use any power supply configuration for what I wanted in (1.) ?

- Do I have to connect bypass capacitors ?