Hello,

This is a follow up question to:

https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/1022706/ads124s08-trouble-reading-conversion-data-with-internal-or-external-reference?tisearch=e2e-sitesearch

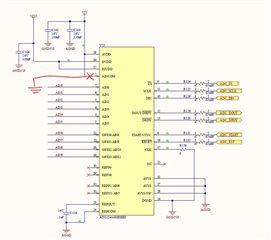

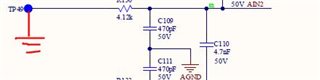

Since posting the previous thread, I determined that I had a bug in my software preventing the Reference Control Register to be written. Since then I have fixed this bug but am still not able to read valid conversion data. I am running the ADC with the internal reference, differential inputs (Ain2 tied to ground and set as the negative input, Ain9 set as the positive inputs signal and tied to a GPIO signal off the ADC). I have the PGA disabled and the internal reference buffers disabled.

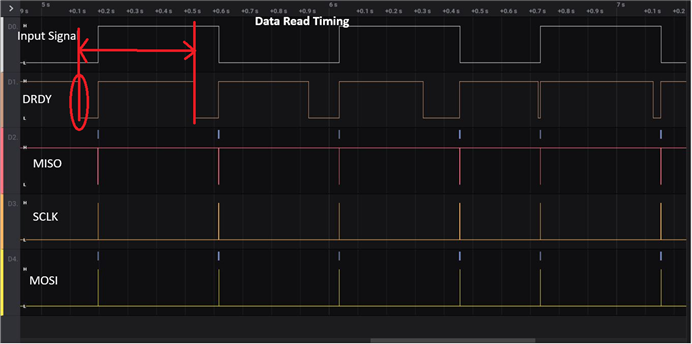

I have a ADC GPIO configured as an output which I have tied to the Ain9 input signal and I toggle it on every conversion reading. Although I would expect to read 0V and 3.3V conversion data based on this GPIO input, I continuously get conversion results that do not match what I expect. Occasionally, I will get results that look like they may be correct but that could just be a coincidence. I am using the slowest data rate of 2.5 SPS for debugging and am polling the DRDY pin for read timing.

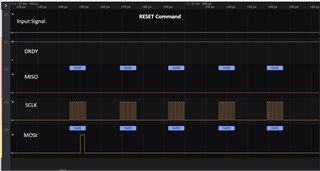

Here are some screen shots of my coms:

Initialization (There is a 3.7 ms delay between all initialization commands):

- Reset Command

- Configure System Reg

- Enable Send Status

- Enable CRC

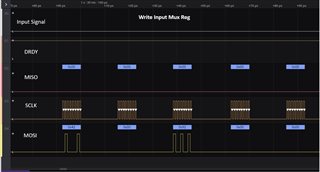

- Configure Input Mux Reg

- Ain2 = negative input

- Ain9 = positive input

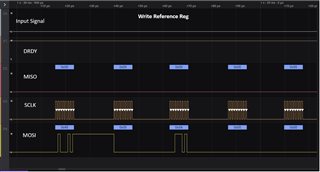

- Configure Reference Reg

- Internal reference always on

- Use internal 2.5V reference

- Disable both reference buffers

- Configure GPIO Data Reg

- GPIO 1 = Output

- Set GPIO 1 = high

- Configure GPIO Config Reg

- Set Ain7 as GPIO (GPIO-1)

- Configure Data Rate Reg

- Set to 2.5 SPS

- Read back Reference Reg for debug

- Start Command

Reading Conversion Data:

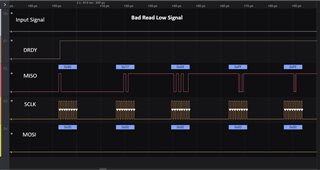

- Bad low signal reading in through Ain9: Conversion results = 1,550,847

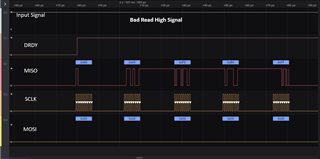

- Bad high signal reading in through Ain9: Conversion results = 6,946,233

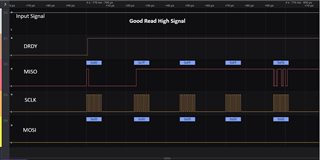

- Good low signal reading through Ain9? Conversion results = 124,865

- Good high signal reading though Ain9? Conversion results = 8,388,607

- Overall conversion reads showing timing