Other Parts Discussed in Thread: THS4501, , THS4502, THS4541, THS4520, THS4503

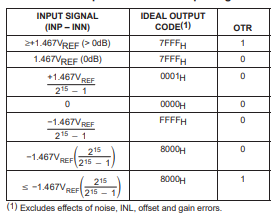

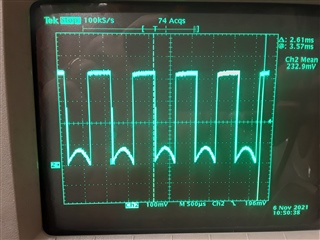

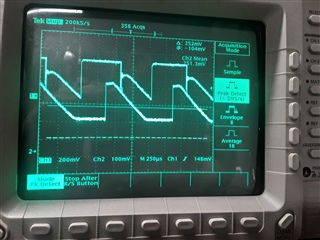

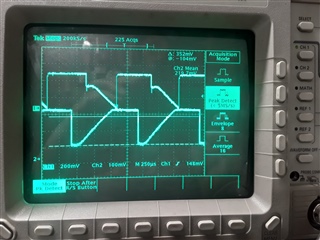

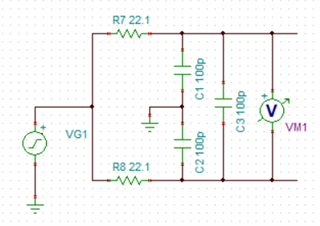

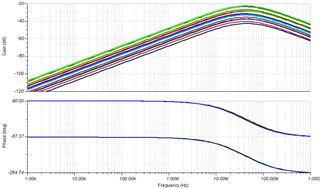

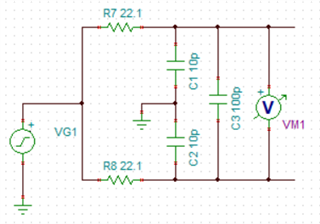

I am using the reference design recommendation in my circuit with the THS4501 driving the ADS1605. For any signal voltage below the Vmid level, the ADC output is correct. When the input Voltage exceeds the Vmid level, the ADC output becomes high for the 3 MSBs immediately, The lower bits seem to behave normally. I have the output going to a DAC and the waveform on the DAC is correct when the input is below the Vmid reference and at full scale when above it, which is what I would expect with the 3 MSBs being high. I cannot understand what can cause this behavior. Any help as to what to look for would be greatly appreciated.

Thank you,

Howard