Other Parts Discussed in Thread: ADC12DJ3200

Hi team

This is in continuation to my previous post https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/1056907/adc12dj3200evm-sync-signal-is-always-low/3921297#3921297

Since my SYNC status is high and LINK is up, I am trying different internal patterns of ADC12DJ3200. Ramp pattern, transport layer pattern, K28.5 works fine. But when i am trying repeated ILA pattern and D21.5 pattern i am not getting expected results. When i am selecting D21.5 pattern, my SYNC status is always low and link is never up. JESD register x208 reads value 04.

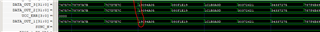

In case of repeated ILA pattern, as per data sheet "In this test mode, the JESD204B link layer operates normally, except that the ILA sequence (ILAS) repeats

indefinitely instead of starting the data phase" but i am getting below waveforms at my end. Highlighted is the portion of data where initial ILA sequence ends, i cant see repetition of ILA sequence in the waveform.

any clues?

Regards

Rohit