Other Parts Discussed in Thread: TSW1418EVM, TSW14DL3200EVM

Hi

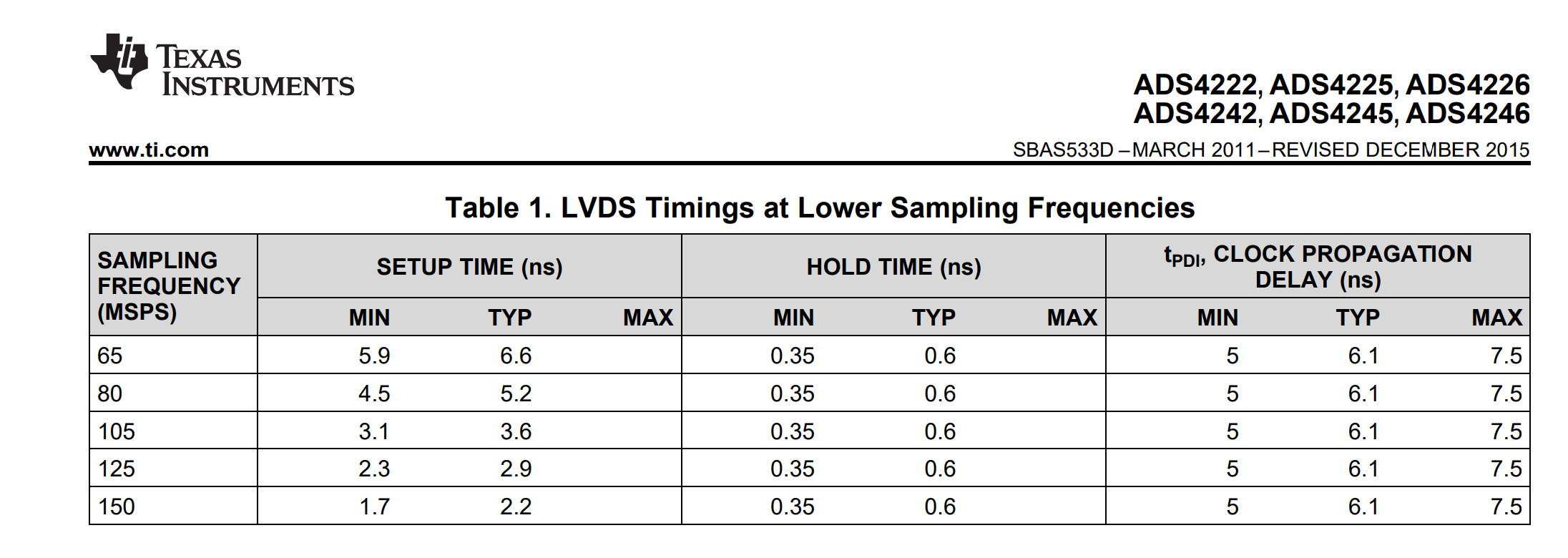

I have read instructions in SLAA545(Interfacing Altera FPGAs to ADS4249 and DAC3482 (TIDA-00069 Reference Guide)) about interfacing ADS42XX boards to FPGA developments boards. I have read the Datasheet and I placed the constraints needes. However I'm not getting good timing (it's functional at least). I'm sampling at approximately 80MSPS so:

create_clock -period 10.000 -name aclk -waveform {0.000 5.000} [get_ports -filter { NAME =~ "*aclk*" && DIRECTION == "IN" }]

create_clock -period 13.468 -name ADC_CLK [get_ports {FMC_LA[17]}]

create_clock -period 13.468 -name ADC_CLK_LAUNCH -waveform {3.367 16.835}

create_generated_clock -name ADC_GEN_CLOCK -source [get_pins PLLE2_BASE_inst/CLKIN1] -multiply_by 1 [get_pins PLLE2_BASE_inst/CLKOUT0]

set_input_delay -clock [get_clocks ADC_CLK_LAUNCH] -min -network_latency_included -source_latency_included -2.767 [get_ports {{FMC_LA[14]} {FMC_LA[29]} {FMC_LA[25]} {FMC_LA[24]} {FMC_LA[21]} {FMC_LA[22]}}]

set_input_delay -clock [get_clocks ADC_CLK_LAUNCH] -max -network_latency_included -source_latency_included -1.833 [get_ports {{FMC_LA[14]} {FMC_LA[29]} {FMC_LA[25]} {FMC_LA[24]} {FMC_LA[21]} {FMC_LA[22]}}]

set_input_delay -clock [get_clocks ADC_CLK_LAUNCH] -min -network_latency_included -source_latency_included -2.767 [get_ports {{FMC_LA[19]} {FMC_LA[15]} {FMC_LA[16]} {FMC_LA[11]} {FMC_LA[12]} {FMC_LA[7]}}]

set_input_delay -clock [get_clocks ADC_CLK_LAUNCH] -max -network_latency_included -source_latency_included -1.833 [get_ports {{FMC_LA[19]} {FMC_LA[15]} {FMC_LA[16]} {FMC_LA[11]} {FMC_LA[12]} {FMC_LA[7]}}]

However i'm getting hold slack issues. I placed IODELAY blocks, but hold slack is intact. How I can time the ninterface properly?