Hi Expert,

My customer have an issue that is not enough output amplitude with ADC09QJ1300EVM.

Test condition1 (no issue)

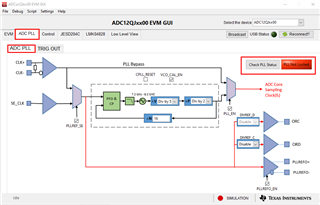

GUI : OnBoard 50M Ref, Fs=500Msps, JMODE10

RX_DIV = 16, 32 and 64

Output amplitude is 460mV @RX_DIV=16 (195.3MHz)

Output amplitude is 540mV @RX_DIV=32 (97.7MHz)

Output amplitude is 530mV @RX_DIV=64 (48.8MHz)

Test condition2 (issue)

GUI :OnBoard 50M Ref, Fs=800Msps, JMODE10

RX_DIV = 16, 32 and 64

Output amplitude is 280mV @RX_DIV=16 (312.5MHz)

Output amplitude is 380mV @RX_DIV=32 (156.25MHz)

Output amplitude is 340mV @RX_DIV=64 (78.125MHz)

*It is spec out V DIFF(min) 400m Vpp-DIFF

Also FPGA was not locked PLL at this test condition.

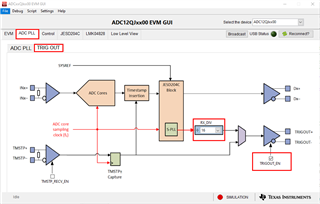

Measurement point

R234(DNP) J9 TRIGOUT+ side and R241(DNP) K9 RTIGOUT- side

Could you please give me your advice?

Thanks

Muk