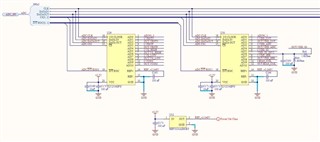

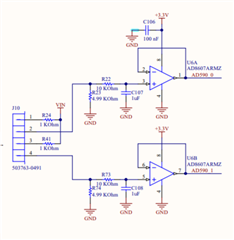

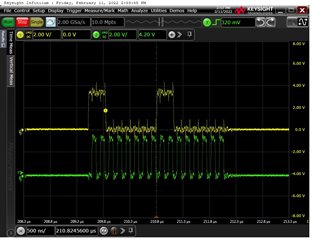

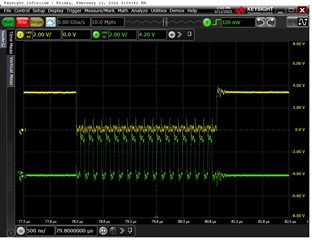

We are witnessing large non-linearities in the conversion output data. Using precision controlled voltage sources (inputs channel 0 and 1 for this test) I am able to see large jumps in output count value corresponding to what should be an LSB change. I am suspicious of the the 4 LSB bits as I often see a +/-16 bit jump in the output conversion data. I am giving the conversion plenty of time as I don't read out the data until ~100ms after EOC goes high. I have tried configuring CFGR2 only at powerup and also interleaving configuration between conversions and still see the conversion errors. Schematic pasted below for reference. Please advise.

Operating Mode: 3.3V supply, 16-bit output length, MSB first, Unipolar, external 2.048V reference, EOC, Normal Mode.