Hi Team,

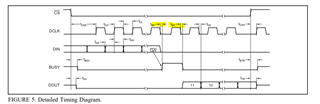

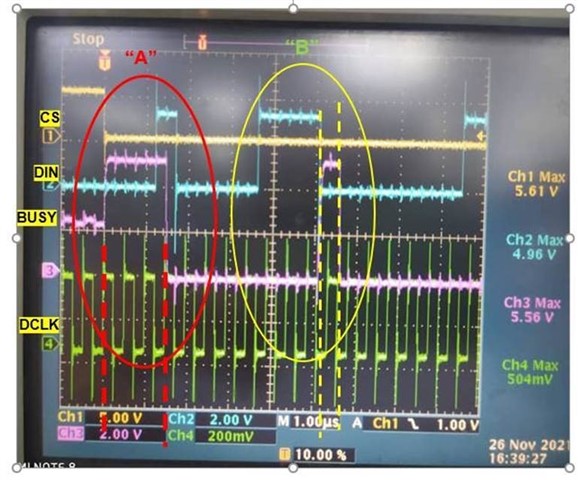

We have some questions for the SPI behavior during working with the customer. The waveform below is capture from the ADS7844 SPI bus.

- We noticed the waveform is changing state on different edge of the clock signal (red rising edge & yellow dotted failing edge)

- Din control bit is being send to ADC while ADC is still BUSY – acceptable ?

- tBD data sheet spec max 100ns vs measured tBD (A waveform) is 200ns

- tCSS data sheet spec min 50ns vs measured tCSS (A waveform)is 0ns

Any idea how ADS7844 will respond to such waveform, we are getting very intermittence failure (consistent failed on certain channel, and not able to repeat the failure when we tested several days later), we would expect the failures to be more consistent, could you please kindly advise on these? Thank you.

Best regards,

Mike